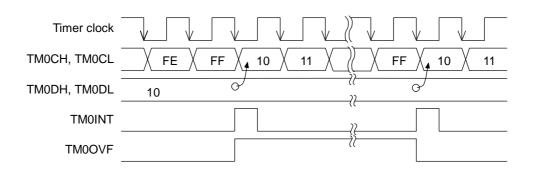

PEUL63611-02

# ML63611 User's Manual

**CMOS 4-bit microcontroller**

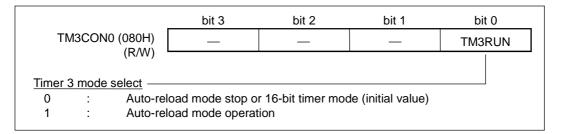

Preliminary

**SECOND EDITION**

**ISSUE DATE: Jun. 2001**

#### NOTICE

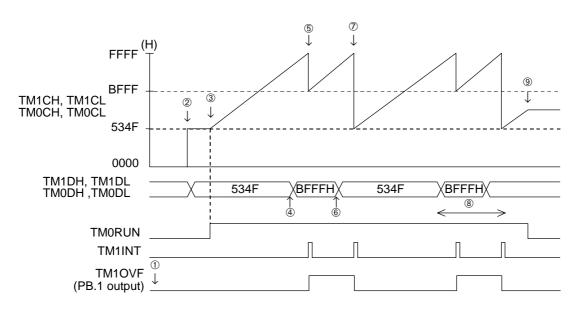

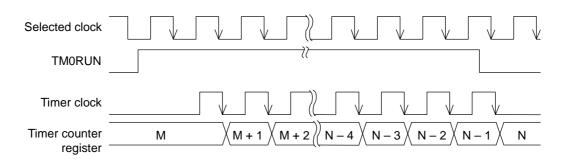

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2001 Oki Electric Industry Co., Ltd.

## Preface

This manual describes the hardware of Oki's original CMOS 4-bit microcontroller ML63611.

Refer to the "nX-4/250, 300 Core Instruction Manual" for details of the 4-bit CPU core nX-4/250 which is built in the ML63611.

The manuals related to the ML63611 is shown below.

- nX-4/250, 300 Core Instruction Manual: Describes the base architecture and instruction set of nX-4/250 core and nX-4/300 core.

- SASM63K User's Manual: Describes the structured assembler operation and assembler language specification.

- Dr.63611 User's Manual: Describes the hardware of the emulator.

- DT63K Debugger User's Manual: Describes the debugger commands and the hardware of the simulator.

- MOGTOOL Mask Option Generator User's Manual: Describes the mask option settings and the generator operation.

This document is subject to change without notice.

| Classification  | Notation                                                                                                                                        | Description                                                                                                                                                                                                                                                          |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ■ Numeric value | xxh, xxH<br>xxb                                                                                                                                 | Represents a hexadecimal number.<br>Represents a binary number.                                                                                                                                                                                                      |

| ■ Unit          | word, W<br>byte, B<br>nibble, N<br>mega-, M<br>kilo-, K<br>kilo-, k<br>milli-, m<br>micro-, µ<br>nano-, n<br>second, s (lower case)<br>KB<br>MB | 1 word = 16 bits<br>1 byte = 2 nibbles = 8 bits<br>1 nibble = 4 bits<br>$10^{6}$<br>$2^{10} = 1024$<br>$10^{3} = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second<br>1 KB = 1 kilobyte = 1024 bytes<br>1 MB = 1 megabyte = $2^{20}$ bytes<br>= 1,048,576 bytes |

| Symbol          | Note:                                                                                                                                           | Gives more information about mistakable items.                                                                                                                                                                                                                       |

| ■ Terminology   | "H" level<br>"L" level                                                                                                                          | Indicates high side voltage signal levels $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics.<br>Indicates low side voltage signal levels $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics.                                    |

## Notation

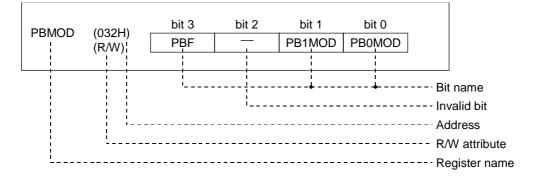

■ Register description

Invalid bit R/W attribute When read, a value of "1" is always obtained. Write operations are invalid.

"R" indicates data can be read and "W" indicates data can be written.

# Contents

| Chapter 1. Overview                                                                               | 1-1 |

|---------------------------------------------------------------------------------------------------|-----|

| 1.1 Overview                                                                                      | 1-1 |

| 1.2 Features                                                                                      |     |

| 1.3 Mask Options                                                                                  |     |

| 1.4 Function List                                                                                 |     |

| 1.5 Block Diagram                                                                                 |     |

| 1.6 Pin Configuration                                                                             |     |

| 1.6.1 ML63611 Pin Configuration                                                                   |     |

| 1.7 Pin Descriptions                                                                              |     |

| 1.7.1 Descriptions of the Basic Functions of Each Pin                                             |     |

| 1.7.2 Descriptions of the Secondary Functions of Each Pin                                         |     |

| 1.7.3 Handling of Unused Pins                                                                     |     |

| 1.8 Basic Timing                                                                                  |     |

| 1.8.1 Basic Timing of CPU Operation                                                               |     |

| 1.8.2 Port I/O Basic Timing                                                                       |     |

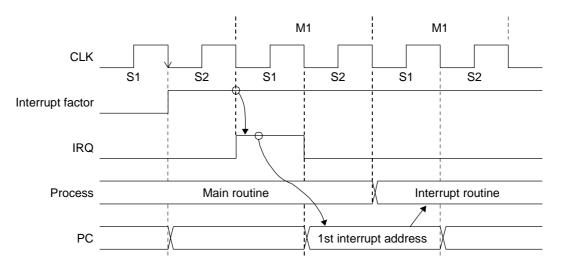

| 1.8.3 Interrupt Basic Timing                                                                      |     |

|                                                                                                   | 25  |

| Chapter 2. CPU and Memory Spaces                                                                  | 2-1 |

| 2.1 Overview                                                                                      | 2-1 |

| 2.1 Overview                                                                                      |     |

| 2.2 Accumulator (A)                                                                               |     |

| 2.2.1 Accumulator (A)                                                                             |     |

| 2.2.2.1 Carry Flag (C)                                                                            |     |

| 2.2.2.1 Carly Flag (C)                                                                            |     |

|                                                                                                   |     |

|                                                                                                   |     |

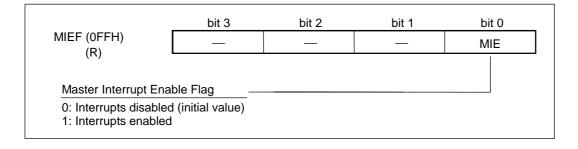

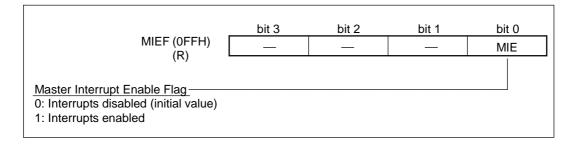

| 2.2.3 Master Interrupt Enable Flag (MIE)                                                          |     |

| 2.2.4 Current Bank Register (CBR), Extra Bank Register (EBR), HL Register (HL), XY Register (XY). |     |

| 2.2.5 Program Counter (PC)                                                                        |     |

| 2.2.6 RA Registers (RA3, RA2, RA1, RA0)                                                           |     |

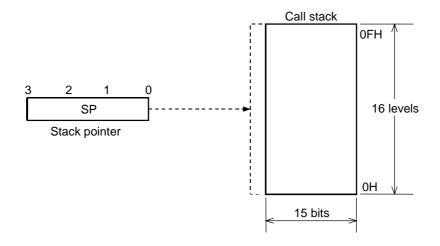

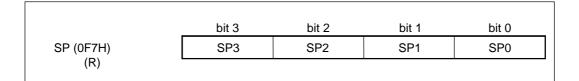

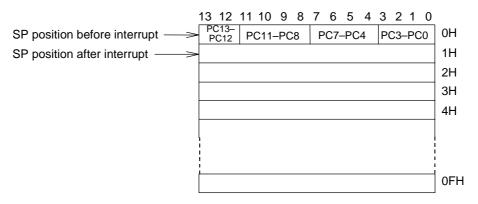

| 2.2.7 Stack Pointer (SP) and Call Stack                                                           |     |

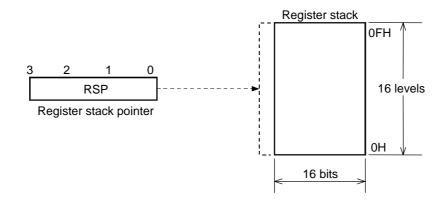

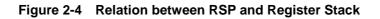

| 2.2.8 Register Stack Pointer (RSP) and Register Stack                                             |     |

| 2.3 Memory Spaces                                                                                 |     |

| 2.3.1 Program Memory Space                                                                        |     |

| 2.3.2 Data Memory Space                                                                           | 2-8 |

| Chapter 3. CPU Control Functions                                                                  | 3-1 |

| 3.1 Overview                                                                                      | 3-1 |

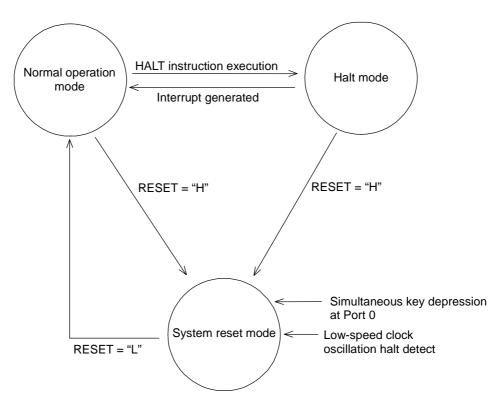

| 3.2 System Reset Mode (RST)                                                                       |     |

| 3.2.1 Transfer to and State of System Reset Mode                                                  |     |

| 3.3 Halt Mode                                                                                     |     |

| 3.3.1 Transfer to and State of Halt Mode                                                          |     |

| 3.3.2 Halt Mode Release                                                                           |     |

|                                                                                                   |     |

|                                                                                                   |     |

| 3.3.2.2 Release of Halt Mode by RESET Pin                                                         |     |

| 3.3.3 Melody Data Interrupt and Halt Mode Release                                                 |     |

| 3.3.4 Note Concerning HALT Instruction                                                            |     |

| Chapter 4. Interrupt (INT)                        | 4-1  |

|---------------------------------------------------|------|

| 4.1 Overview                                      | 4-1  |

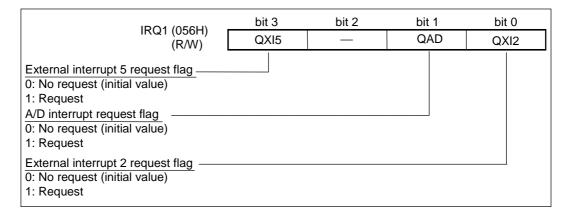

| 4.2 Interrupt Registers                           |      |

| 4.3 Interrupt Sequence                            |      |

| 4.3.1 Interrupt Processing                        | 4-11 |

| 4.3.2 Return from an Interrupt Routine            | 4-12 |

| 4.3.3 Interrupt Hold Instructions                 | 4-12 |

| Chapter 5. Clock Generator Circuit (OSC)          | 5-1  |

| 5.1 Overview                                      |      |

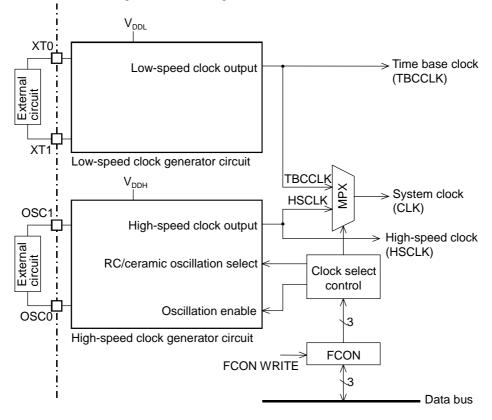

| 5.2 Clock Generator Circuit Configuration         |      |

| 5.3 Low-Speed Clock Generator Circuit             |      |

| 5.4 High-Speed Clock Generator Circuit            |      |

| 5.5 System Clock Control                          |      |

| 5.6 Frequency Control Register (FCON)             |      |

| 5.7 System Clock Select Timing                    | 5-7  |

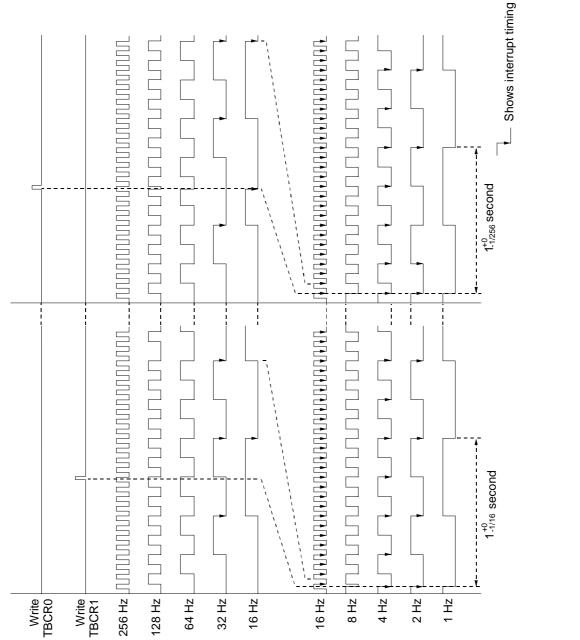

| Chapter 6. Time Base Counter (TBC)                | 6-1  |

| 6.1 Overview                                      |      |

| 6.2 Time Base Counter Configuration               | 6-1  |

| 6.3 Time Base Counter Registers                   | 6-2  |

| 6.4 Time Base Counter Operation                   | 6-2  |

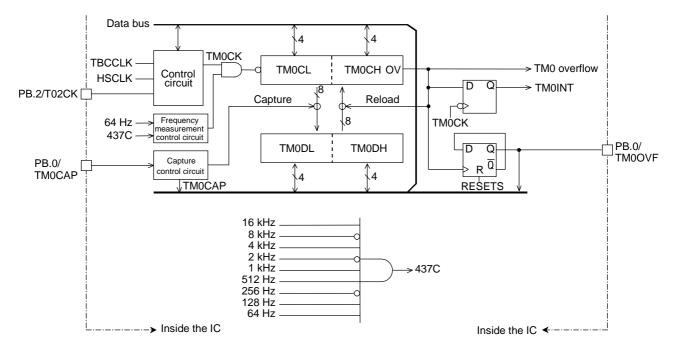

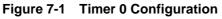

| Chapter 7. Timers (TIMER)                         | 7-1  |

| 7.1 Overview                                      |      |

| 7.2 Timer Configuration                           |      |

| 7.3 Timer Registers                               |      |

| 7.4 Timer Operation                               |      |

| 7.4.1 Timer Clock                                 |      |

| 7.4.2 Timer Data Registers                        | 7-14 |

| 7.4.3 Timer Counter Registers                     | 7-14 |

| 7.4.4 Timer Interrupt Requests and Overflow Flags | 7-15 |

| 7.4.5 Auto-Reload Mode Operation                  | 7-16 |

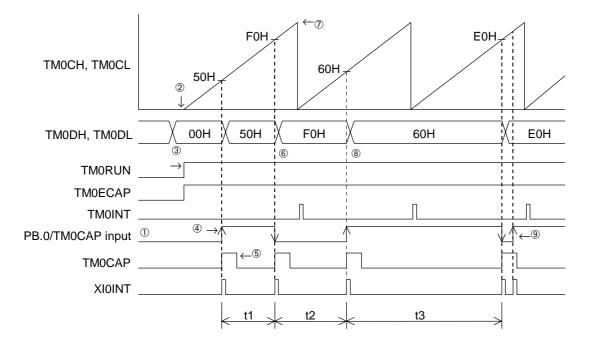

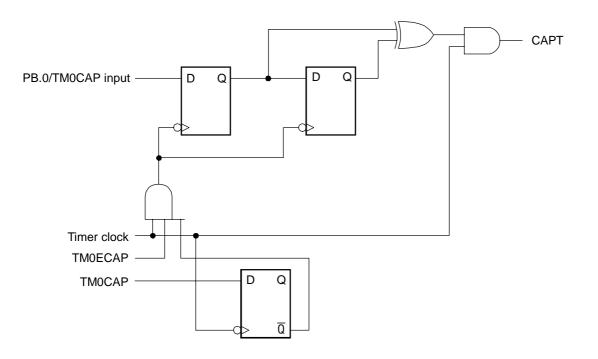

| 7.4.6 Capture Mode Operation                      |      |

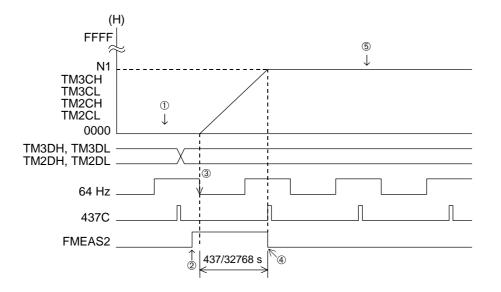

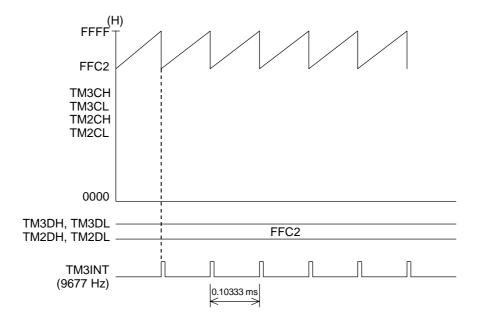

| 7.4.7 Frequency Measurement Mode Operation        | 7-21 |

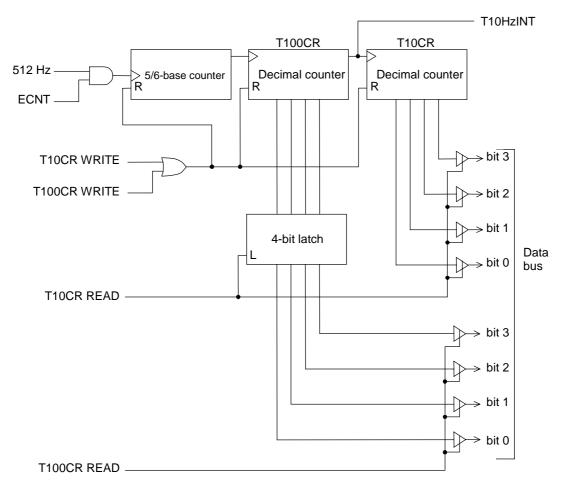

| Chapter 8. 100 Hz Timer Counter (100HzTC)         | 8-1  |

| 8.1 Overview                                      | 8-1  |

| 8.2 100 Hz Timer Counter Configuration            |      |

| 8.3 100 Hz Timer Counter Registers                |      |

| 8.4 100 Hz Timer Counter Operation                | 8-3  |

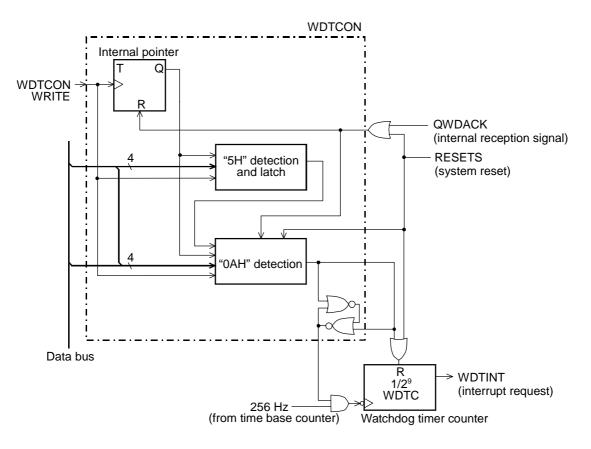

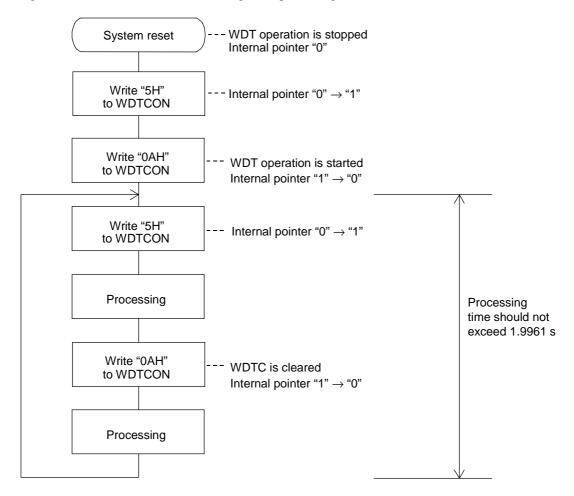

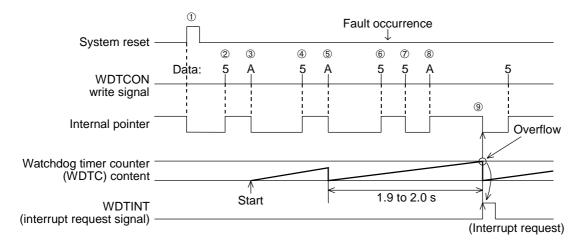

| Chapter 9. Watchdog Timer (WDT)                   | 9-1  |

| 9.1 Overview                                      | 9-1  |

| 9.2 Watchdog Timer Configuration                  |      |

| 9.3 Watchdog Timer Control Register (WDTCON)      |      |

| 9.4 Watchdog Timer Operation                      |      |

|                                                   |      |

## Chapter 10. Ports (INPUT, I/O PORT)

| 1 | 0- | -1 |

|---|----|----|

|   | v  | 1  |

12-1

13-1

| 10.1 Overview                                                      |      |

|--------------------------------------------------------------------|------|

| 10.2 Ports List                                                    |      |

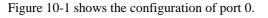

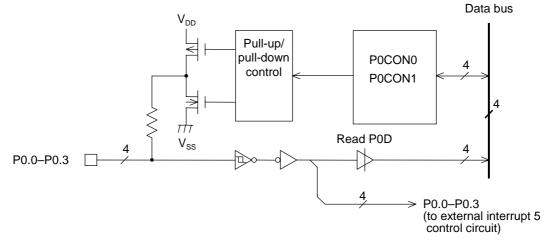

| 10.3 Port 0 (P0.0–P0.3)                                            |      |

| 10.3.1 Port 0 Configuration                                        |      |

| 10.3.2 Port 0 Registers                                            |      |

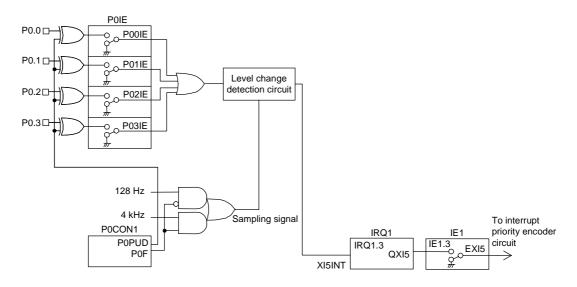

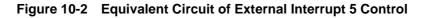

| 10.3.3 Port 0 External Interrupt Function (External Interrupt 5)   |      |

| 10.4 Port A (PA.0–PA.3)                                            |      |

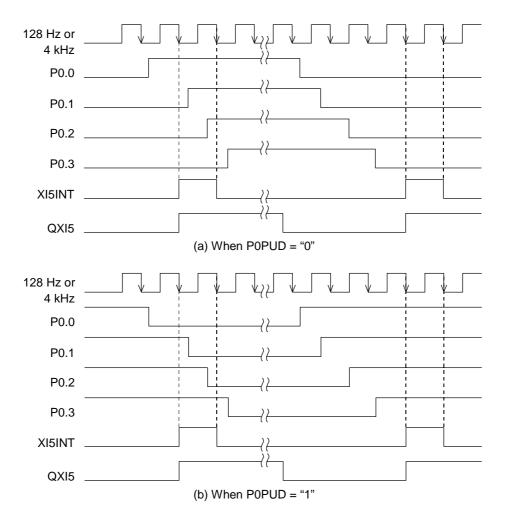

| 10.4.1 Port A Configuration                                        |      |

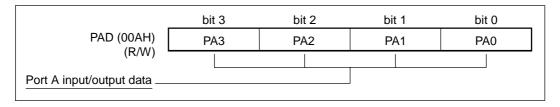

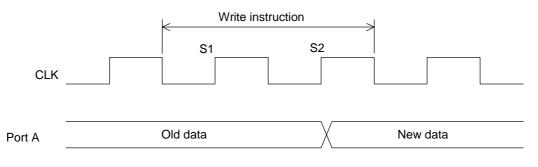

| 10.4.2 Port A Registers                                            |      |

| 10.5 Port B (PB.0–PB.3)                                            |      |

| 10.5.1 Port B Configuration                                        |      |

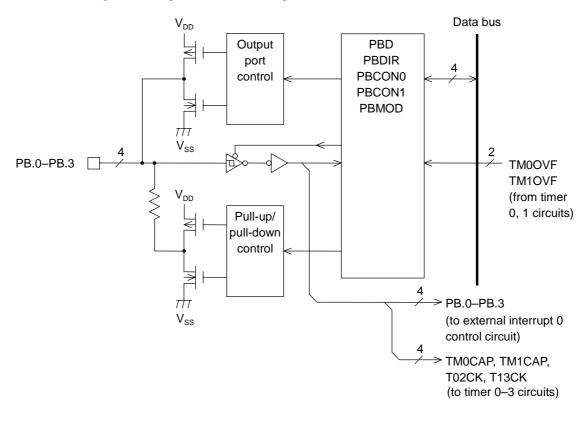

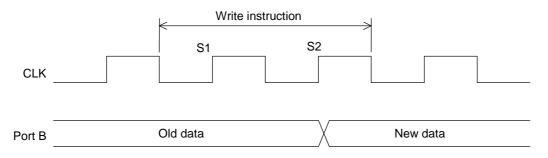

| 10.5.2 Port B Registers                                            |      |

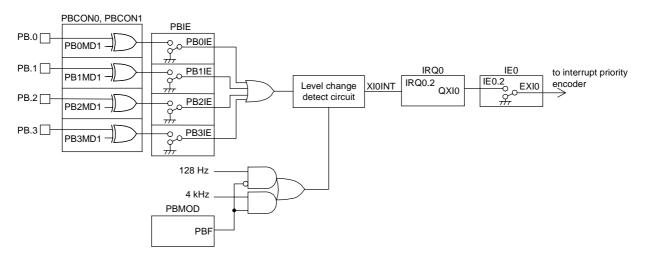

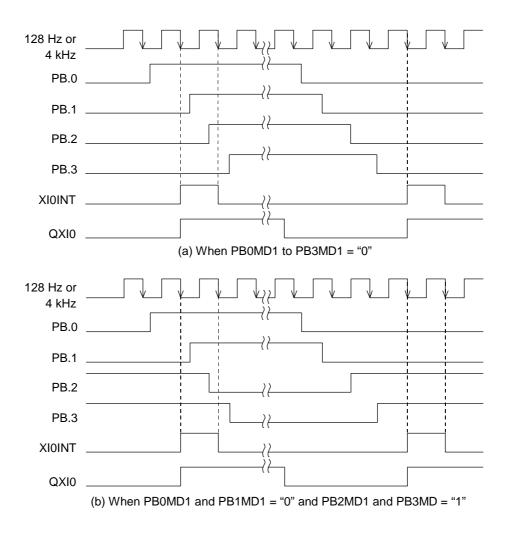

| 10.5.3 Port B External Interrupt Function (External Interrupt 0)   |      |

| 10.6 Port C (PC.0–PC.3)                                            |      |

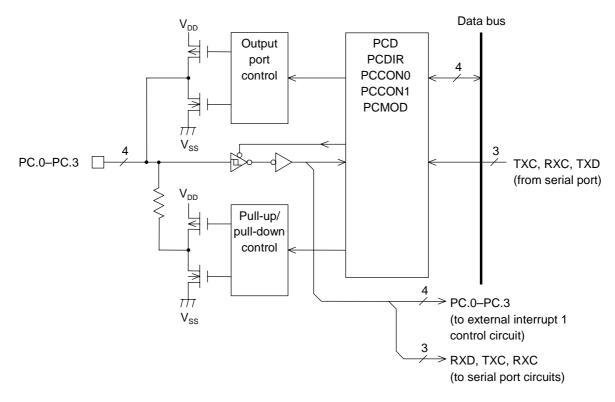

| 10.6.1 Port C Configuration                                        |      |

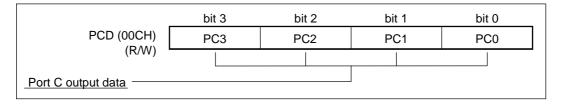

| 10.6.2 Port C Registers                                            |      |

| 10.6.3 Port C External Interrupt Function (External Interrupt 1)   |      |

| 10.7 Port E (PE.0–PE.3)                                            |      |

| 10.7.1 Port E Configuration                                        |      |

| 10.7.2 Port E Registers                                            |      |

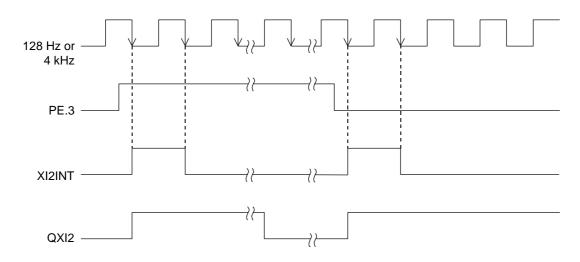

| 10.7.3 Port E.3 External Interrupt Function (External Interrupt 2) |      |

|                                                                    |      |

| Chapter 11. Melody Driver (MELODY)                                 | 11-1 |

| 11.1 Overview                                                      |      |

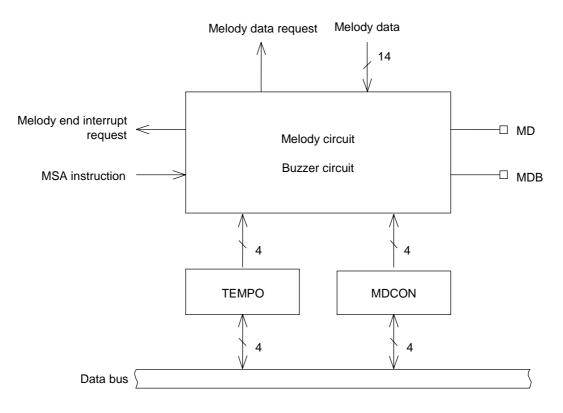

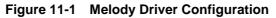

| 11.2 Melody Driver Configuration                                   |      |

| 11.3 Melody Driver Registers                                       |      |

| 11.4 Melody Circuit Operation                                      |      |

| 11.4.1 Tempo Data                                                  |      |

| 11.4.2 Malady Data                                                 |      |

| 11.4.1 | Tempo Data                         | 11-5 |

|--------|------------------------------------|------|

| 11.4.2 | Melody Data                        | 11-6 |

|        | Melody Circuit Application Example |      |

|        | Buzzer Circuit Operation           |      |

|        |                                    |      |

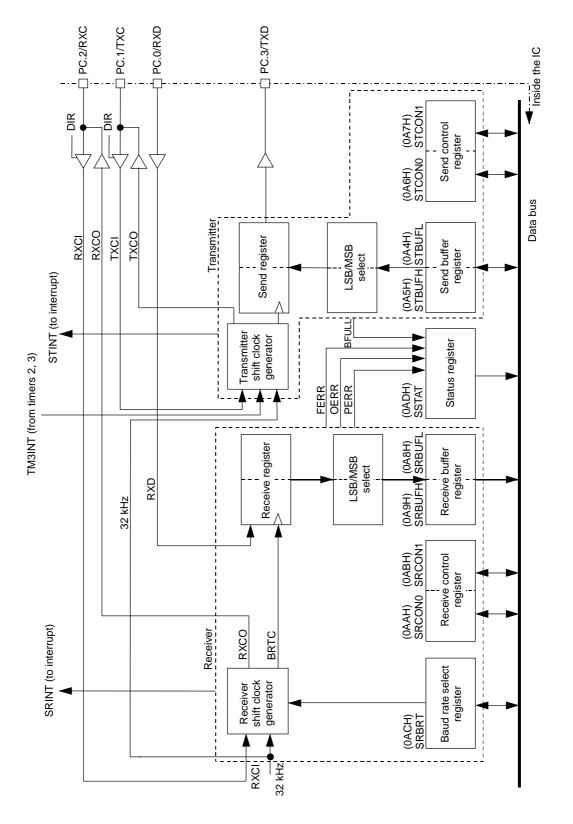

# Chapter 12. Serial Port (SIO)

| 12.1 Overview                               |  |

|---------------------------------------------|--|

| 12.2 Serial Port Configuration              |  |

| 12.3 Serial Port Registers                  |  |

| 12.4 Serial Port Operation Description      |  |

| 12.4.1 Data Format                          |  |

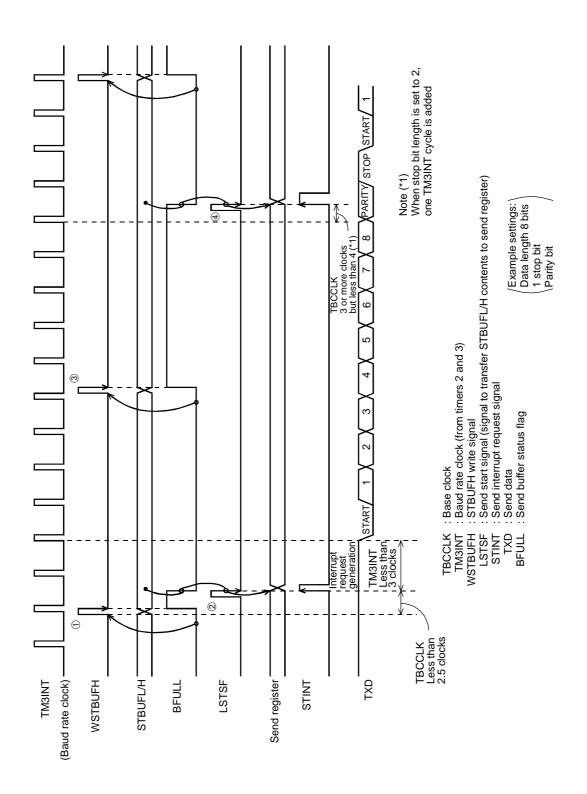

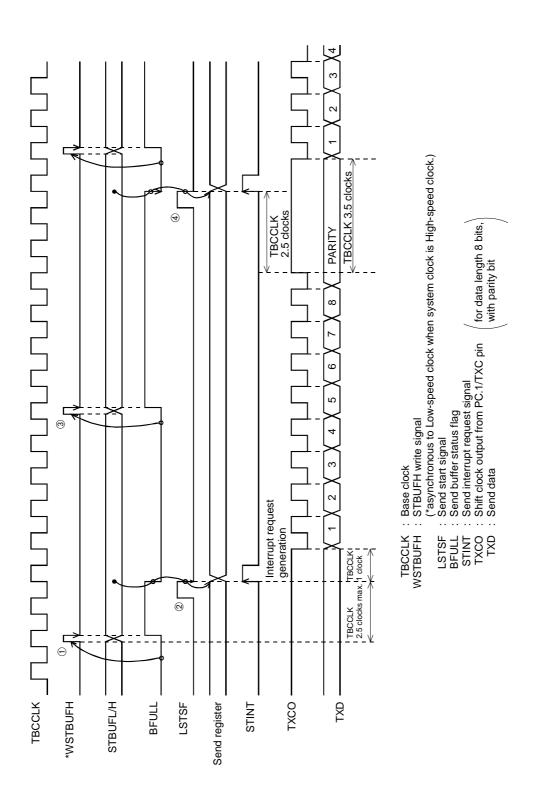

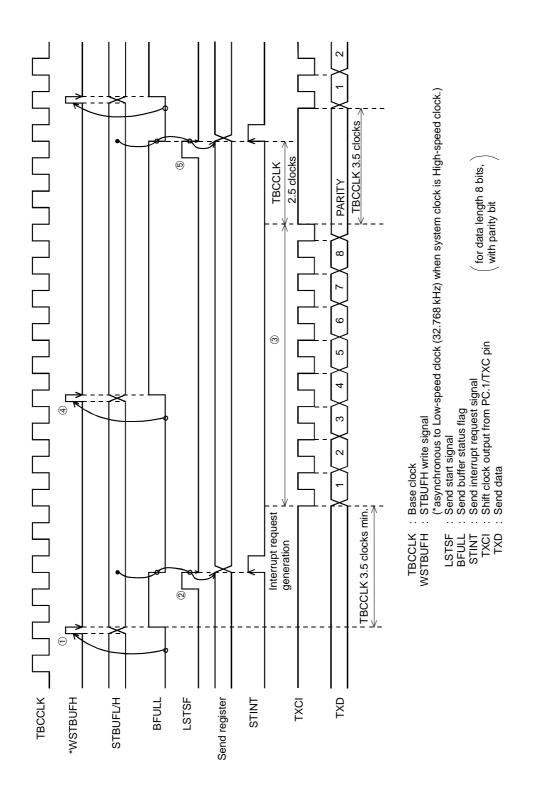

| 12.4.2 Send Operation Description           |  |

| 12.4.3 Receive Operation Description        |  |

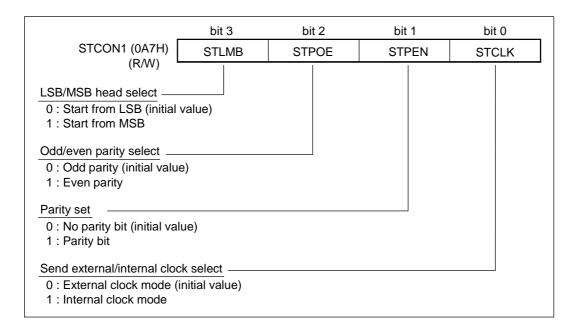

| 12.5 Send/Receive Data LSB/MSB First Select |  |

| 12.5.1 Selecting Send Data LSB/MSB First    |  |

| 12.5.2 Selecting Receive Data LSB/MSB First |  |

|                                             |  |

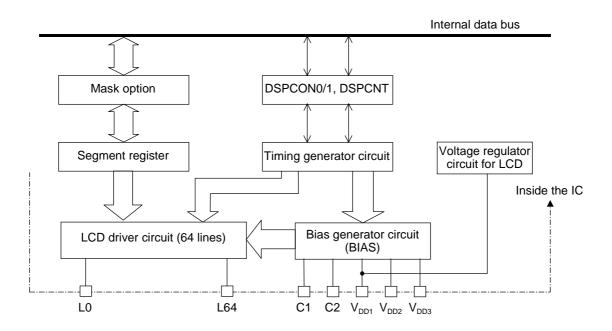

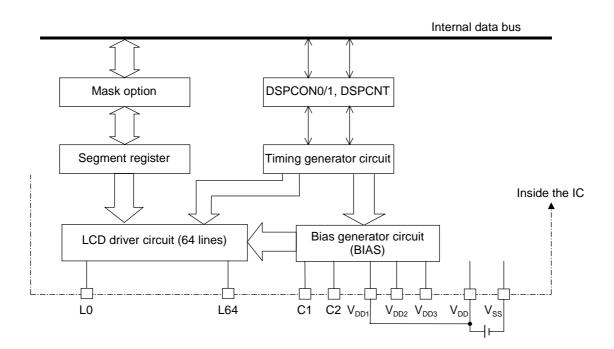

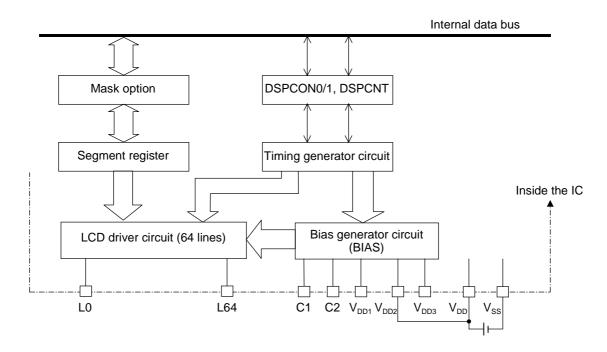

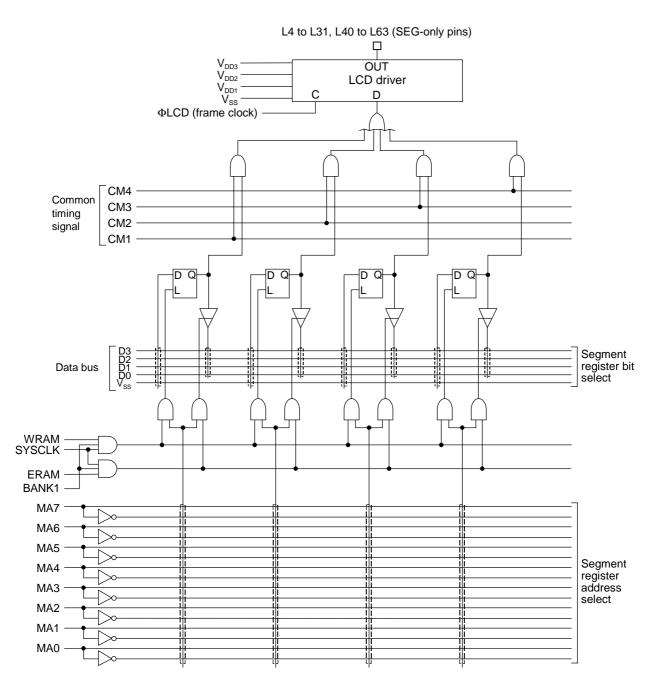

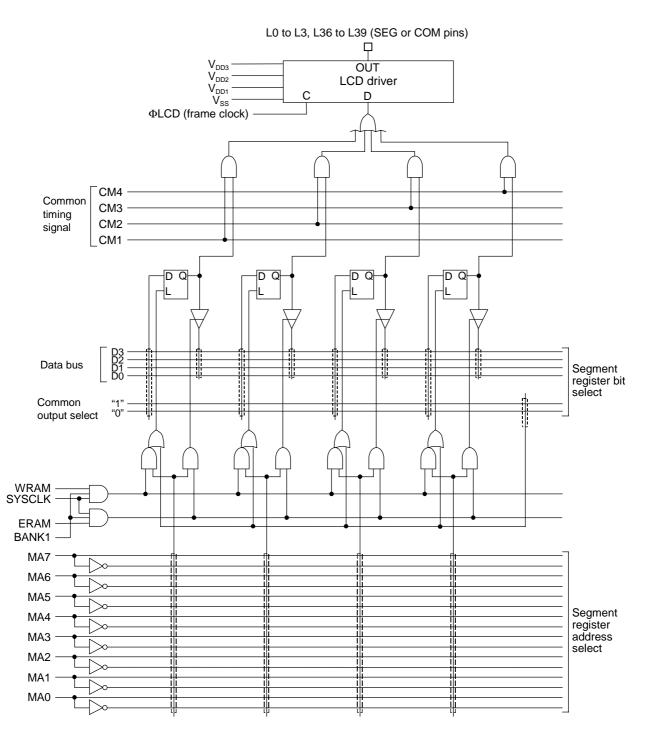

## Chapter 13. LCD Driver (LCD)

| 13.1 | Overview                             |       |

|------|--------------------------------------|-------|

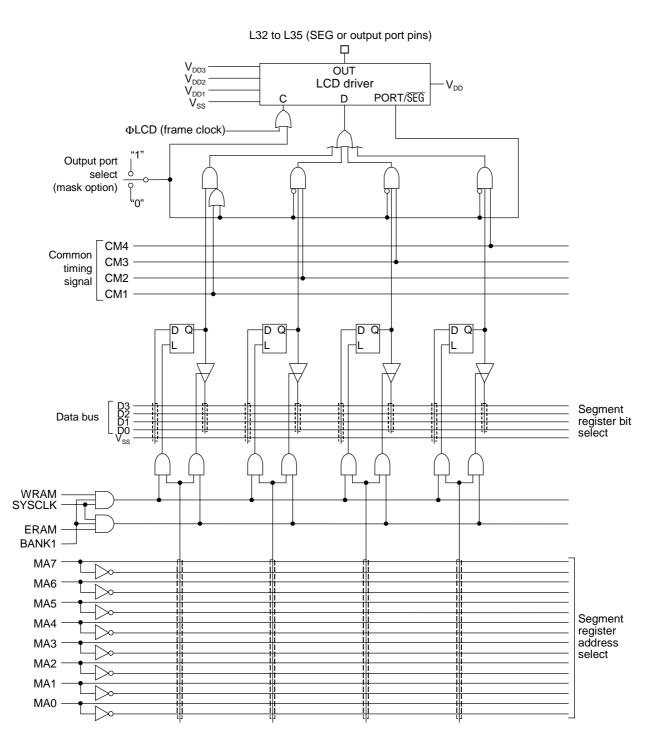

|      | LCD Driver Configuration             |       |

|      | LCD Driver Registers                 |       |

| 13.4 | LCD Driver Operation                 |       |

| 13.5 | Output Port Selection by Mask Option |       |

| 13.6 | Bias Generator Circuit (BIAS)        |       |

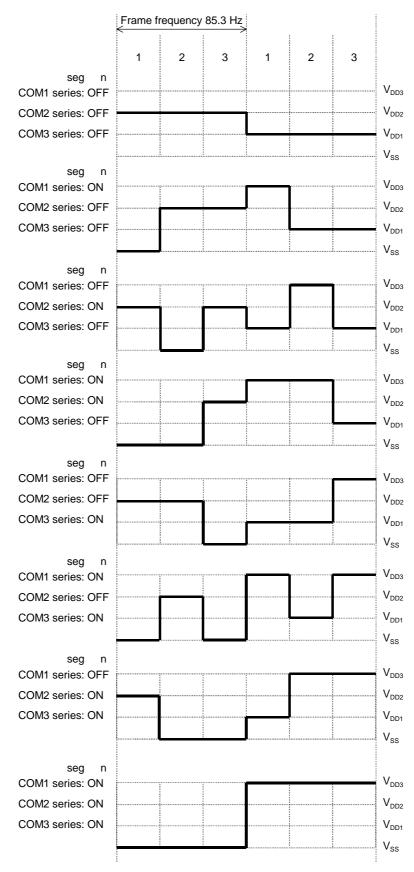

| 13.7 | LCD Driver Output Waveform           | 13-17 |

|      |                                      |       |

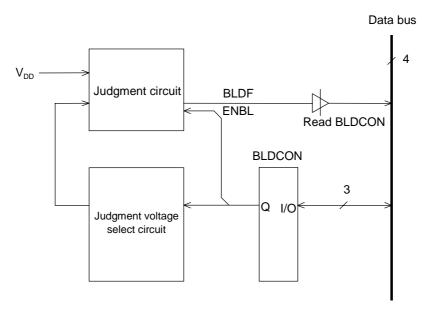

| Chapter 14. Battery Low Detect Circuit (BLD)          | 14-1 |

|-------------------------------------------------------|------|

| 14.1 Overview                                         |      |

| 14.2 Battery Low Detect Circuit Configuration         |      |

| 14.3 Judgment Voltage                                 |      |

| 14.4 Battery Low Detect Circuit Register              |      |

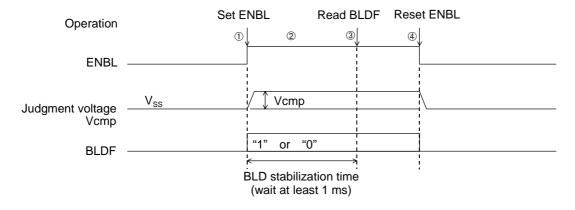

| 14.5 Battery Low Detect Circuit Operation             |      |

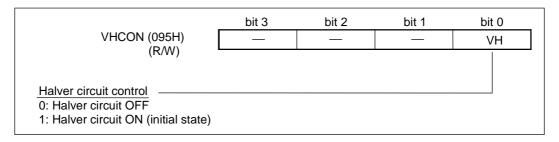

| Chapter 15. Power Supply Circuit (POWER)              | 15-1 |

| 15.1 Overview                                         |      |

| 15.1.1 Precautions in Using the Halver Circuit        |      |

| 15.2 Power Supply Circuit Related Register            |      |

| 15.3 Power Supply Circuit Configuration               |      |

| 15.3.1 OPTION A Power Supply Circuit Configuration    |      |

| 15.3.2 Operation of the OPTION A Power Supply Circuit |      |

| 15.3.3 OPTION B Power Supply Circuit Configuration    |      |

| 15.3.4 Operation of the OPTION B Power Supply Circuit |      |

| 15.3.5 OPTION C Power Supply Circuit Configuration    | 15.7 |

| 15.3.5 | OPTION C Power Supply Circuit Configuration    | 13-7 |

|--------|------------------------------------------------|------|

| 15.3.6 | Operation of the OPTION C Power Supply Circuit | 15-8 |

|        | OPTION D Power Supply Circuit Configuration.   |      |

|        | Operation of the OPTION D Power Supply Circuit |      |

|        | -F                                             |      |

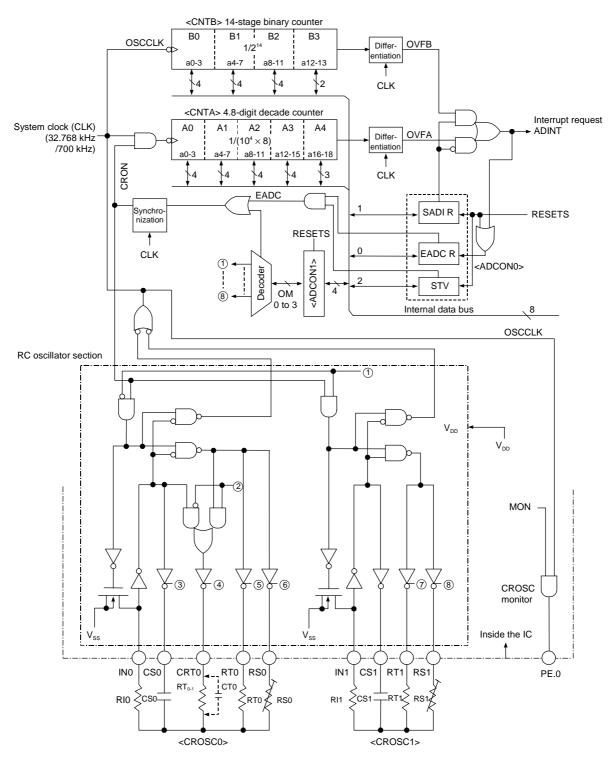

## Chapter 16. A/D Converter (ADC)

16-1

| 16.1 Overview                            |  |

|------------------------------------------|--|

| 16.2 A/D Converter Configuration         |  |

| 16.3 Operation of A/D Converter          |  |

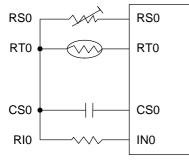

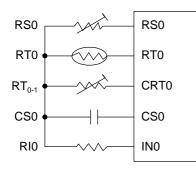

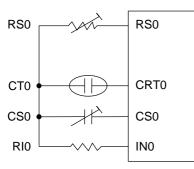

| 16.3.1 RC Oscillation Circuit            |  |

| 16.3.2 Counter A/B Reference Mode        |  |

| 16.3.3 Example of Usage of A/D Converter |  |

| 16.3.4 RC Oscillation Monitor            |  |

| 16.4 Registers Related to A/D Converter  |  |

## Appendixes

| Appendix A | List of Special Function Registers | Appendix-1  |

|------------|------------------------------------|-------------|

| Appendix B | Input/Output Circuit Configuration | Appendix-5  |

| Appendix C | Peripheral Circuit Examples        | Appendix-7  |

| Appendix D | Instruction List                   | Appendix-11 |

Chapter 1

# Overview

## 1. Overview

## 1.1 Overview

The ML63611 is a CMOS 4-bit microcontroller using Oki's original CPU core nX-4/250.

The ML63611 is provided with the mask options of eight items of selection including (1.5 V or 3.0 V) power supply specifications and (With or Without) the regulator circuit for the LCD bias reference voltage.

When a 3.0 V power supply specification is selected, the halver circuit can be used to decrease power consumption. The halver circuit cannot be used when a 1.5 V power supply specification is selected.

When "With the regulator circuit for the LCD bias reference voltage" is selected, the LCD bias reference voltage will be generated based on the output voltage of the regulator circuit. When "Without the regulator circuit for the LCD bias reference voltage" is selected, the LCD bias reference voltage will be generated based on the power supply voltage; for this reason, the LCD bias voltage decreases as the power supply voltage decreases, causing the display density of the LCD panel to thin down.

The ML63611 has incorporated in it an 8K-word program memory, a 1K-nibble data memory, four input ports, four output ports (only when the mask option of LCD driver pins is selected), 16 I/O ports, a melody circuit, a serial port, four 8-bit timers, and a 64-segment LCD driver (60 segment lines and 4 common lines, max.). (A part of the SEG pins can also be selected as output port pins or COM pins depending on the mask option.)

Note:

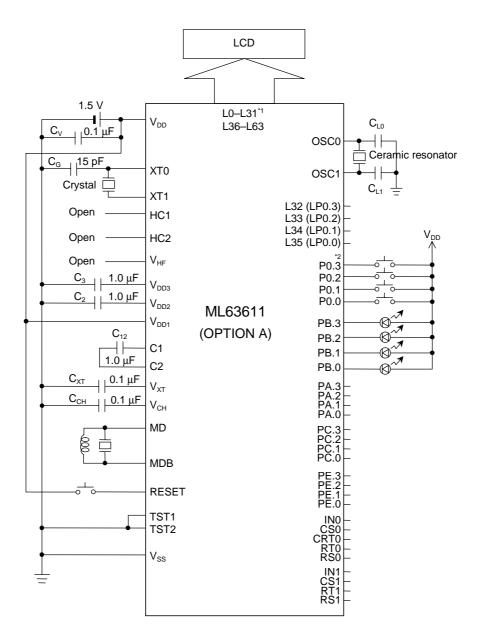

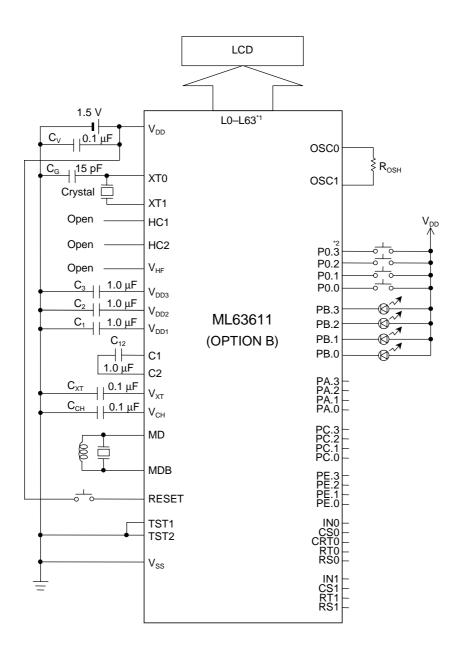

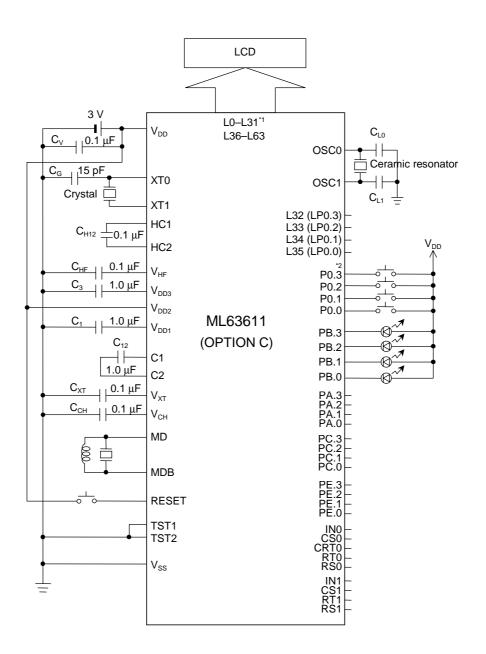

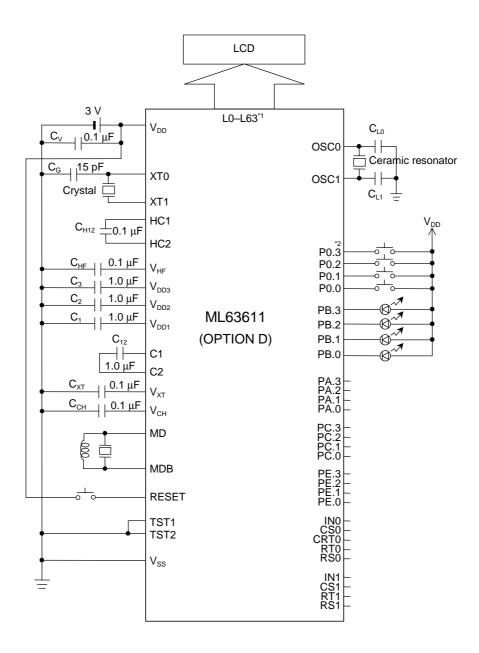

In this manual, for convenience of description, the symbols OPTION A, OPTION B, OPTION C, and OPTION D are used in accordance with the mask option selection of a power supply specification (1.5 V or 3.0 V) and the regulator circuit for the LCD bias reference voltage (With or Without), as shown below.

- OPTION A: 1.5 V power supply specification (halver circuit disabled), without the regulator circuit for the LCD bias reference voltage

- OPTION B: 1.5 V power supply specification (halver circuit disabled), with the regulator circuit for the LCD bias reference voltage

- OPTION C: 3.0 V power supply specification (halver circuit enabled), without the regulator circuit for the LCD bias reference voltage

- OPTION D: 3.0 V power supply specification (halver circuit enabled), with the regulator circuit for the LCD bias reference voltage

## 1.2 Features

The ML63611 has the following features.

- a. Extensive instruction set

- 407 instructions

Transfer, rotate, increment/decrement, arithmetic operations, compare, logic operations, mask operations, bit operations, ROM table reference, stack operations, flag operations, jump, conditional branch, call/return, control

b. Wide variety of addressing modes

- Indirect addressing mode for 4 types of data memory with current bank register, extra bank register, HL register and XY register

- Data memory bank internal direct addressing mode

#### c. Processing speed

•

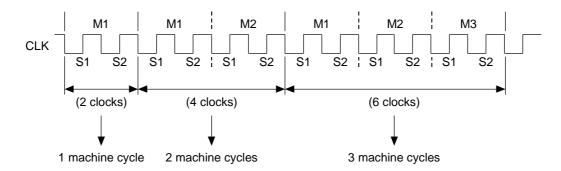

- 2 clocks per machine cycle, with most instructions executed in 1 machine cycle

- Minimum instruction execution time:

61 µs (@ 32.768 kHz system clock) 10 µs (@ 200 kHz system clock)

2.86 µs (@ 700 kHz system clock)

d. Clock generator circuit

- Low-speed clock:

- Crystal oscillation (32.768 kHz)

High-speed clock: OPTION A, OPTION B: RC oscillation (200 kHz max.) OPTION C, OPTION D: Ceramic oscillation or RC oscillation selected with software (700 kHz max.)

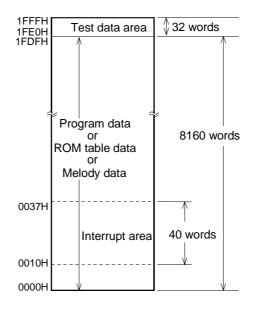

e. Program memory space

- 8K words

- The basic instruction length is 16 bits per word.

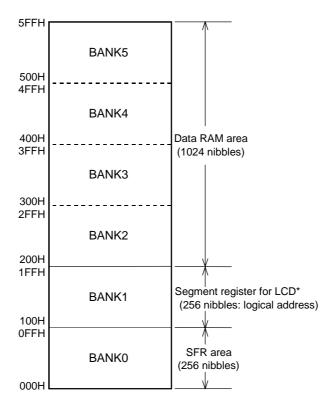

#### f. Data memory space

• 1024 nibbles

### g. Stack level

- Call stack level: 16

- Register stack level: 16

#### h. Ports

Input port (Port 0.0 to Port 0.3):

| mput p  |                                                | 5).                                                                                     |                           |                                    |  |  |  |  |  |

|---------|------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------|------------------------------------|--|--|--|--|--|

|         | Selectable a                                   | as input with pull-up r                                                                 | esistor/high-impedance    | input                              |  |  |  |  |  |

|         | Provided w                                     | vith the reset function                                                                 | that resets the system    | when there is a simultaneous key   |  |  |  |  |  |

|         | depression of multiple bits (2, 3, or 4 bits). |                                                                                         |                           |                                    |  |  |  |  |  |

| Output  | port: Selectable                               | ort: Selectable as N-channel open drain output/CMOS output                              |                           |                                    |  |  |  |  |  |

|         |                                                | Enabled only when the SEG pins (L32 to L35) are selected as the output port by the mask |                           |                                    |  |  |  |  |  |

|         | option.                                        |                                                                                         |                           |                                    |  |  |  |  |  |

| Input-o | output port (Port A.0 to                       | Port A.3, Port B.0 to                                                                   | Port B.3, Port C.0 to P   | ort C.3, Port E.0 to Port E.3):    |  |  |  |  |  |

|         | Selectable a                                   | as input with pull-up r                                                                 | esistor/input with pull-c | down resistor/high-impedance input |  |  |  |  |  |

|         | Selectable a                                   | as P-channel open dra                                                                   | in output/N-channel ope   | en drain output/CMOS output/high-  |  |  |  |  |  |

|         | impedance                                      | output                                                                                  |                           |                                    |  |  |  |  |  |

| Numbe   | er of ports:                                   |                                                                                         |                           |                                    |  |  |  |  |  |

|         | -                                              | Input ports                                                                             | Output ports              | Input-output ports                 |  |  |  |  |  |

| -       | Chip products                                  | 1 port $\times$ 4 bits                                                                  | 1 port $\times$ 4 bits    | 4 ports $\times$ 4 bits            |  |  |  |  |  |

(mask option)

### ----

### i. Melody output

|   | y surput                     |                                  |

|---|------------------------------|----------------------------------|

| • | Melody frequency:            | 529 Hz to 2979 Hz (@ 32.768 kHz) |

| • | Tone length:                 | 63 varieties                     |

| • | Tempo:                       | 15 varieties                     |

| • | Melody data:                 | Stored in program memory         |

| • | Buzzer driver signal output: | 4 kHz (@ 32.768 kHz)             |

|   |                              |                                  |

## j. LCD driver

Segment-type LCD drivers built-in

The following pin modes can be specified for L0 to L63 by the mask option generator setting. (Refer to the "MOGTOOL Mask Option Generator User's Manual".)

"•" in the table below indicates that that particular function can be selected.

|                  | L0 to L3 | L4 to L31 | L32 to L35 | L36 to L39 | L40 to L63 |

|------------------|----------|-----------|------------|------------|------------|

| SEG Pins         | •        | •         | •          | •          | •          |

| COM Pins         | ●*1      | _         | —          | ●*1        | —          |

| Output Port Pins | _        | _         | ●*2        | _          | —          |

- \*1 Can be selected as a COM pin in 1-bit unit (L0 to L3, L36 to L39). A maximum of four pins can be selected as COM pins.

- \*2 Can be selected as an output port in 4-bit unit (L32 to L35). N-channel open drain output or CMOS output can be specified for each bit.

Number of segments: 64 (60 SEG. × 4 COM. Max.)

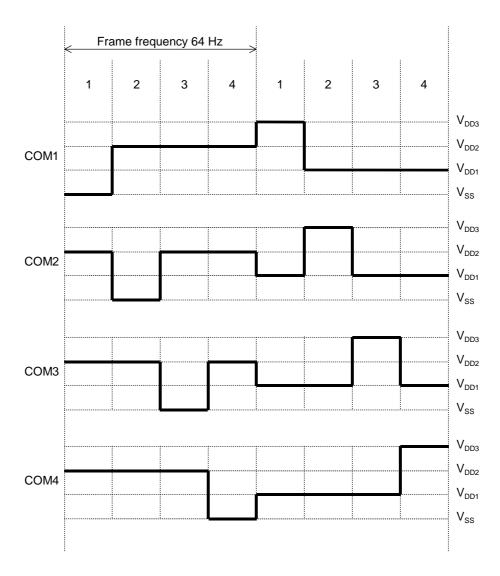

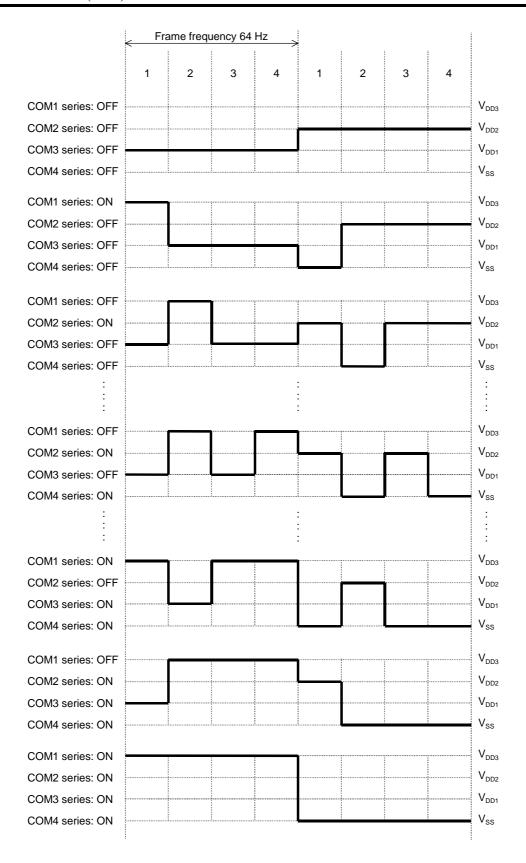

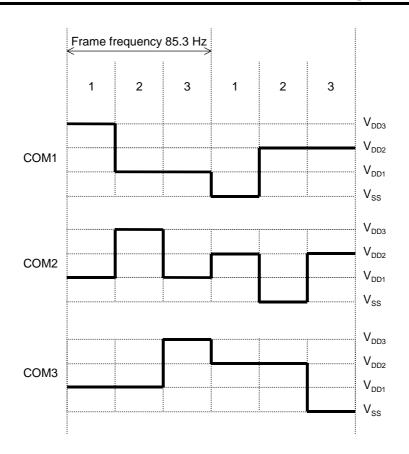

| Duty            | : 1/1 to 1/4 duty (fixed to 1/2 duty when at 1/2 bias)                          |

|-----------------|---------------------------------------------------------------------------------|

| Bias            | : Selectable as 1/2 or 1/3 bias                                                 |

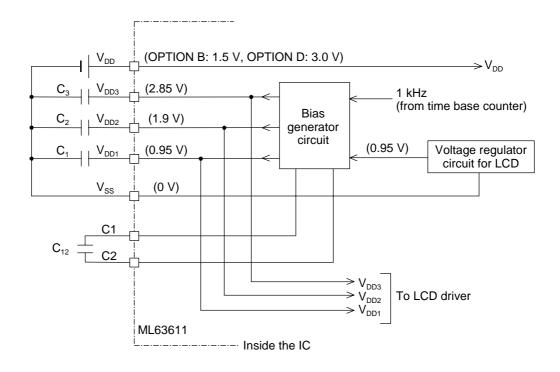

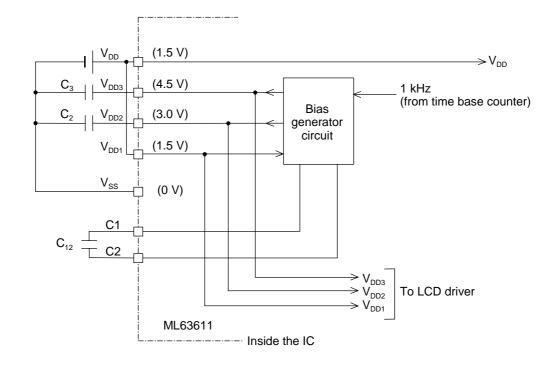

|                 | OPTION B, OPTION D: Regulator circuit used (0.95/1.90/2.85 V)                   |

|                 | OPTION A, OPTION C: Regulator circuit not used (directly connected to the power |

|                 | supply voltage (1.5/3.0/4.5 V))                                                 |

| Frame frequency | : 64 Hz (at 1/1, 1/2, 1/4 duty), 85.3 Hz (at 1/3 duty)                          |

| Contrast        | : OPTION B, OPTION D: Adjustable up to 16 levels (in steps of 0.03 V)           |

|                 | OPTION A, OPTION C: Adjustment not available                                    |

| Display modes   | : Selectable as all-ON mode/all-OFF mode/power down mode/normal display mode    |

k. RC oscillation type A/D converter

• 2 channels (time sharing is used)

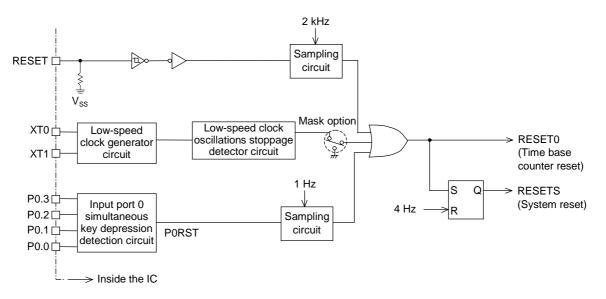

1. System reset function

- System reset by RESET pin (2 kHz sampling function provided)

- System reset that resets the system when the combined bits (2, 3, or 4 bits) of the input port (Port 0) are all set to a "H" level

(Whether system reset is disabled or enabled, the number of bits to be combined, and the polarity can be specified by mask option. Refer to the "MOGTOOL Mask Option Generator User's Manual".)

- 2 bits : P0.0, P0.1

- 3 bits : P0.0, P0.1, P0.2

- 4 bits : P0.0, P0.1, P0.2, P0.3

m. Battery check

- Applies to the OPTION C and OPTION D. Does not apply to the OPTION A and OPTION B.

- Function that detects battery low voltage

- Selection of judgment voltage by software (LD1 and LD0 bit settings of BLDCON)

| LD1 | LD0 | Judgment voltage (V) | Accuracy (V) | Comments  |

|-----|-----|----------------------|--------------|-----------|

| 0   | 0   | 1.8 ±0.1             | ±0.1         | Ta = 25°C |

| 0   | 1   | 2.0 ±0.1             | ±0.1         | Ta = 25°C |

| 1   | 0   | 2.4 ±0.1             | ±0.1         | Ta = 25°C |

| 1   | 1   | 2.6 ±0.1             | ±0.1         | Ta = 25°C |

#### n. Timers, counters

- 8-bit timer: 4 channels Selectable as auto-reload mode, capture mode, clock frequency measurement mode

- Watchdog timer: 1 channel

- 100 Hz timer: 1 channel

1/100 sec. measurement possible

- 15-bit TBC: 1 channel

- 1 Hz, 2 Hz, 4 Hz, 8 Hz, 16 Hz, 32 Hz, 64 Hz, 128 Hz signals can be read

#### o. Serial port

- Mode: UART mode, synchronous mode

- Communication speed in UART mode: 1200 bps, 2400 bps, 4800 bps, 9600 bps

- Clock frequency in synchronous mode: 32.768 kHz (internal clock mode); external clock frequency

- Data length: 5 to 8 bits

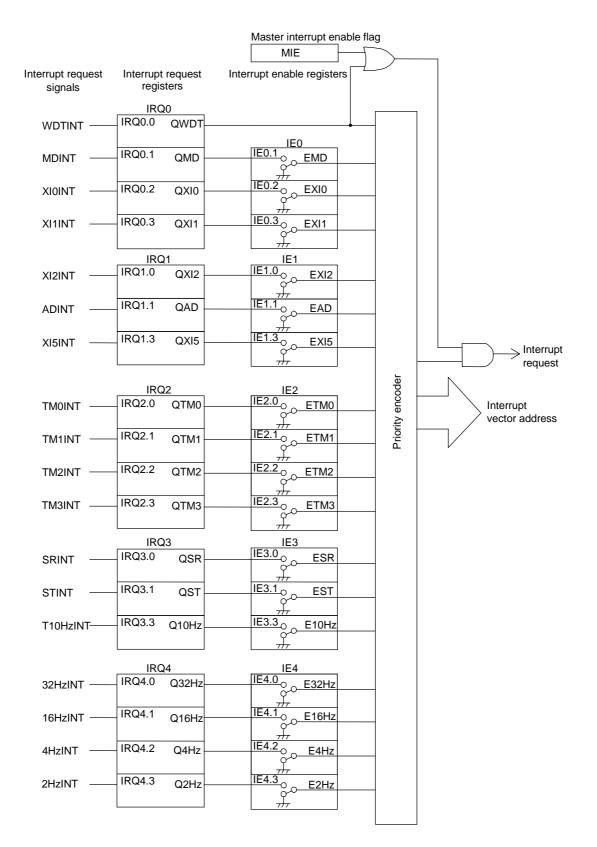

#### p. Interrupt factors

- External interrupt (4 sources) : Selectable as rising edge/falling edge/both rising and falling edges

- Internal interrupt (14 sources) :

- : Watchdog timer interrupt × 1 Melody end interrupt × 1 ADC interrupt × 1 Timer interrupt × 4 Serial port reception interrupt × 1 Serial port transmission interrupt × 1 1/100 timer (10 Hz) interrupt × 1

- Time base interrupt  $\times$  4 (2, 4, 16, and 32 Hz)

#### q. Operating temperature

#### • $-20 \text{ to } +70^{\circ}\text{C}$

### r. Power supply voltage

OPTION A, OPTION B (1.5 V versions): 1.3 to 1.7 V

- Note: The operation will only be at the battery voltage and no voltage halver circuit can be used.

- OPTION C, OPTION D (3.0 V versions): 1.8 to 3.6 V

- Note: It is possible to select by software to use the output of the halver circuit as the power supply of the voltage regulator circuit when the battery voltage is in the range 2.4 to 3.6 V, and to use the battery voltage itself as the power supply of the voltage regulator circuit when the battery voltage is in the range 1.8 to 2.4 V.

- It is possible to detect whether the battery voltage is 2.4 V or 1.8 V using the BLD function.

- When the halver circuit is ON: 2.4 to 3.6 V

- When the halver circuit is OFF: 1.8 to 2.4 V

#### s. Supply current

- In the HALT mode, with the LCD display OFF, low-speed operation, and at normal temperature:

- OPTION A (1.5 V power supply specification, without the regulator circuit for the LCD bias reference voltage): Typ. 1.06 μA, 2.4 μA Max.

- OPTION B (1.5 V power supply specification, with the regulator circuit for the LCD bias reference voltage): Typ. 1.4 μA, 2.8 μA Max.

- OPTION C (3.0 V power supply specification, without the regulator circuit for the LCD bias reference voltage): Typ. 0.53 μA, 1.2 μA Max.

- OPTION D (3.0 V power supply specification, with the regulator circuit for the LCD bias reference voltage): Typ. 0.70 μA, 1.4 μA Max.

#### t. Packages available

| _ | Package        | Product name                                            |

|---|----------------|---------------------------------------------------------|

|   | Chip (116-pad) | ML63611-xxxWA<br>(Here, 'xxx' denotes the code number.) |

| OPTION A (C): | 1.5 V (3.0 V), Without regulator |

|---------------|----------------------------------|

|               | circuit for LCD bias             |

## 1.3 Mask Options

There are eight items in the mask option of the ML63611.

Make the settings for the following items using the MOGTOOL mask option generator. Refer to the "MOGTOOL Mask Option Generator User's Manual" for details of the method of making the settings.

Selection of power supply voltage Select a power supply specification for the power supply voltage to be used as either a 1.5 V power supply specification (1.3 to 1.7 V) or a 3.0 V power supply specification (1.8 to 3.6 V).

Note:

When a 1.5 V power supply specification (OPTION A and OPTION B) is selected, the halver circuit and the battery low detect circuit cannot be used.

Selection of the regulator circuit for the LCD bias reference voltage Select the LCD bias reference voltage as either the output of the regulator circuit or the power supply voltage.

Note:

When power is supplied from the battery:

When "Without the regulator circuit for the LCD bias reference voltage" is selected with the mask option, the LCD bias reference voltage will be generated based on the power supply voltage. When a 1.5 V power supply specification is selected,  $V_{DD1}$  will be the pin for the LCD bias reference voltage, and when a 3.0 V power supply specification is selected,  $V_{DD2}$  will be the pin for the LCD bias reference voltage. In addition, the LCD bias voltage will decrease as the power supply voltage decreases, causing the display density of the LCD panel to thin down. When "With the regulator circuit for the LCD bias reference voltage" is selected, the display density will be kept constant even if the battery voltage decreases.

3) Selection of the initial state of Port 0

Select the initial state of Port 0 as either "input with pull-down resistor" or "input with pull-up resistor". This selection determines the initial value of POPUD (POCON1).

Note:

This selection applies to all four bits and it is not possible to make this selection separately for each bit.

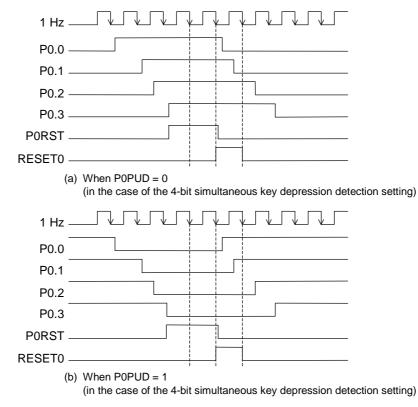

4) Selection of simultaneous key depression reset function of Port 0

Select the simultaneous key depression reset function and the number of bits (pins) that can be pressed simultaneously.

The pins that are set according to the number of bits pressed simultaneously are fixed as follows: 2 bits: P0.0, P0.1; 3 bits: P0.0, P0.1, P0.2; 4 bits: P0.0, P0.1, P0.2, P0.3.

The system reset mode will be entered at the second falling edge of the 1 Hz signal.

5) Selection of MDB pin output voltage level Select whether to make the output voltage level of the melody output pin (MDB: negative logic) either  $V_{DD}$ or  $V_{SS}$  when the melody is OFF. 6) SEG/COM/PORT/DATA selection of the LCD driver pins

It is possible to make the pins L0 to L3 and L36 to L39 either SEG pins or COM pins. However, it is a

maximum of four pins that can be selected as COM pins.

It is possible to make the pins L32 to L35 either SEG pins or output port pins.

The pins L4 to L31 and L40 to L63 are always SEG pins.

The segment register corresponding to the pins L0 to L63 can also be used as a DATA area.

- When the selection is made as output port pins, the selection applies to all four bits.

- When the segment register is selected as the DATA area, the corresponding pins will still be outputting the segment waveforms, and hence should be left open.

- Selection of the register address and data of the LCD driver pins The allocation of the register address and data is set for each LCD driver pin.

Note:

It is not possible to make multiple settings for the same address and the same bit.

Selection of whether or not to detect stoppage of low-speed clock oscillations Select whether or not to detect stoppage of the low-speed clock oscillations and to transfer to the system reset mode.

## 1.4 Function List

Table 1-1 lists the functions of the ML63611. The solid black circles within the chart indicate that the product has the particular function.

| Function                          | Symbol          | OPTION A                                                  | OPTION B                    | OPTION C         | OPTION D     | Referenc<br>page |

|-----------------------------------|-----------------|-----------------------------------------------------------|-----------------------------|------------------|--------------|------------------|

| Power supply voltage              | V <sub>DD</sub> | 1.5 V (1.3 to 1.7                                         | V)                          | 3.0 V (1.8 to 3  | 3.6 V)       | —                |

| STACK RAM                         |                 |                                                           |                             |                  |              | 2-1              |

| Call                              | STACK           | 16 levels                                                 | 2-5                         |                  |              |                  |

| Register                          | STACK           | 16 levels                                                 |                             |                  |              | 2-6              |

| Internal memory                   | Internal memory |                                                           |                             |                  |              | 2-7              |

| Program memory ROM                |                 | 8160 (× 16 bits)                                          |                             |                  |              | 2-7              |

| Data memory                       | RAM             | 1024 (× 4 bits)                                           |                             |                  |              | 2-8              |

| System reset generation circuit   | RST             | 2 kHz sampling f<br>reset function of<br>speed clock osci | Port 0, detect              |                  |              | 3-2              |

| Interrupt                         | INT             | External: 4 source                                        | ces; internal: <sup>2</sup> | 14 sources       |              | 4-1              |

| Clock generator circuit           |                 |                                                           |                             |                  |              | 5-1              |

|                                   | ×-              | Crystal oscillation                                       | n circuit (32.7             | 68 kHz)          |              |                  |

| Low-speed clock                   | ХТ              | 32.768 kHz                                                |                             |                  |              | 5-2              |

|                                   |                 | RC oscillation cir                                        | rcuit, ceramic              | oscillation circ | uit          |                  |

| High-speed clock                  | OSC             | 200 kHz max.                                              |                             | 700 kHz max      |              | 5-3              |

| Time base counter                 | TBC             | 15 bits $\times$ 1 ch                                     | 6-1                         |                  |              |                  |

| Timer                             | TIMER           | 8 bits $\times$ 4 ch                                      |                             |                  |              |                  |

| 100 Hz timer counter              | 100HzTC         | 1 ch                                                      |                             |                  |              |                  |

| Watchdog timer                    | WDT             | 1 ch                                                      |                             |                  |              | 9-1              |

| Port                              | 1               | I                                                         |                             |                  |              | 10-1             |

| Input-only port                   | INPUT PORT      | 1 port × 4 bits                                           |                             |                  |              | _                |

| Port 0                            | P0              | 4 bits (P0.0, P0.1, P0.2, P0.3)                           |                             |                  |              | 10-2             |

| Output-only port                  | OUTPUT PORT     | T 1 port $\times$ 4 bits (selectable by mask option)      |                             |                  |              |                  |

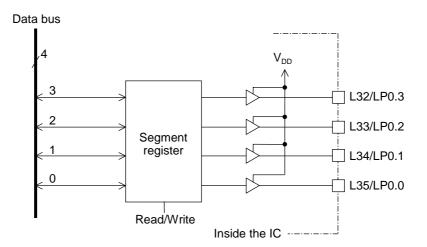

| Port LP                           | LP0             | 4 bits (LP0.0, LP0.1, LP0.2, LP0.3)                       |                             |                  |              | 13-9             |

| Input-output port                 | I/O PORT        | 4 ports × 4 bits                                          |                             |                  |              | _                |

| Port A                            | PA              | 4 bits (PA.0, PA.                                         | 1, PA.2, PA.3               | 3)               |              | 10-7             |

| Port B                            | PB              | 4 bits (PB.0, PB.                                         |                             |                  |              | 10-11            |

| Port C                            | PC              | 4 bits (PC.0, PC.                                         |                             | ,                |              | 10-19            |

| Port E                            | PE              | 4 bits (PE.0, PE.1, PE.2, PE.3)                           |                             |                  |              | 10-27            |

| Melody driver                     | MELODY          | 529 to 2979 Hz                                            |                             | ,                |              | 11-1             |

| Serial port                       | SIO             | Asynchronous (l                                           | JART) or synd               | chronous         |              | 12-1             |

| LCD driver                        | LCD             | 64 segments (60                                           |                             |                  |              | 13-1             |

| Segment register                  | SEGREG          | $256 \times 4$ bits                                       |                             |                  |              | 13-10            |

| Bias generator circuit            | BIAS            | 1/2 or 1/3 bias                                           |                             |                  |              | 13-12            |

| Battery low detect circuit        | BLD             |                                                           | _                           | 1.8 V, 2.0 V,    | 2.4 V, 2.6 V | 14-1             |

| Power supply circuit (POWER)      | 1               | 11                                                        |                             |                  |              | 15-1             |

| Halver circuit                    | V/H             |                                                           |                             | •                | •            | 15-1             |

| Voltage regulator circuit         | 1               | II                                                        |                             | 1                | I            | 15-1             |

| For internal logic circuits       | V/R1            |                                                           | •                           |                  | •            | 15-1             |

| For low-speed oscillation         | V/R2            | •                                                         | •                           | •                | •            | 15-1             |

| For LCD bias generation reference | V/R3            | _                                                         | •                           | _                | •            | 15-1             |

| A/D converter                     | ADC             | 2 channels, of R                                          | C oscillation t             | vpe              | 1            | 16-1             |

| Table 1-1 | Function List | Ł |

|-----------|---------------|---|

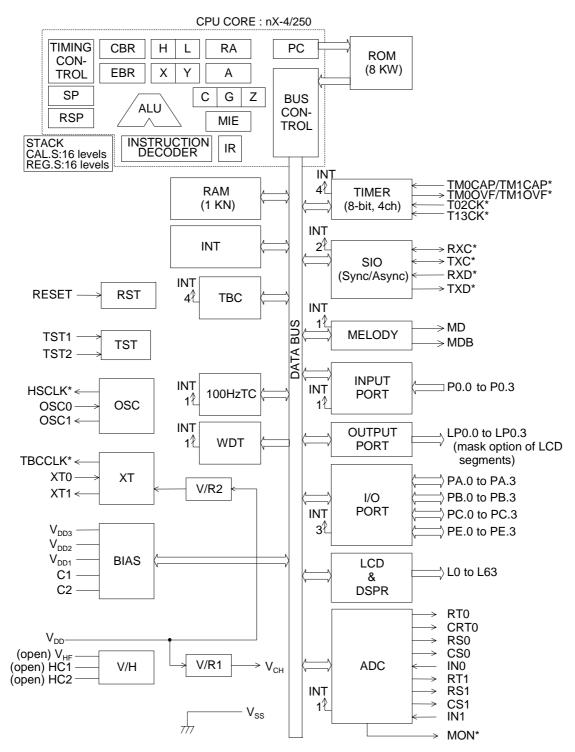

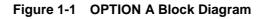

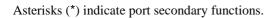

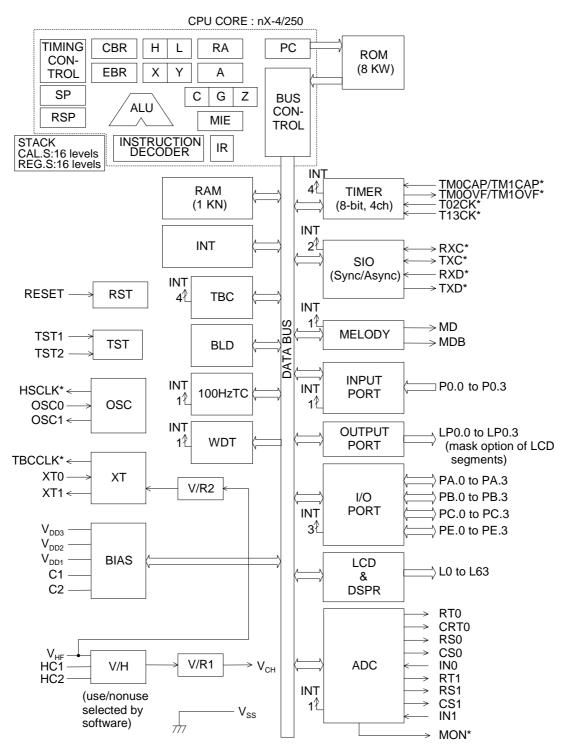

## 1.5 Block Diagram

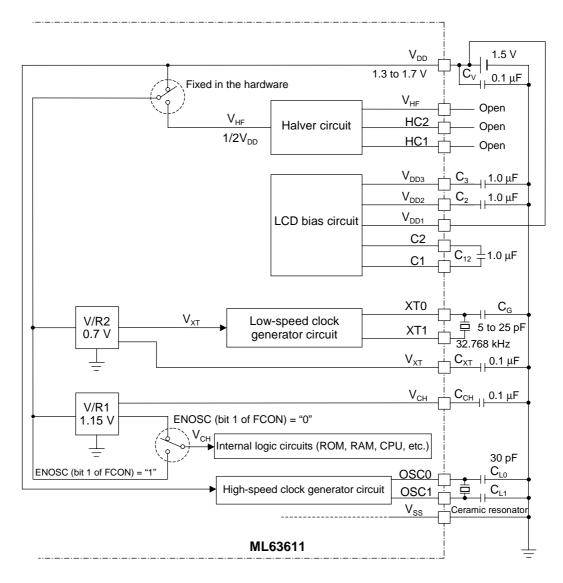

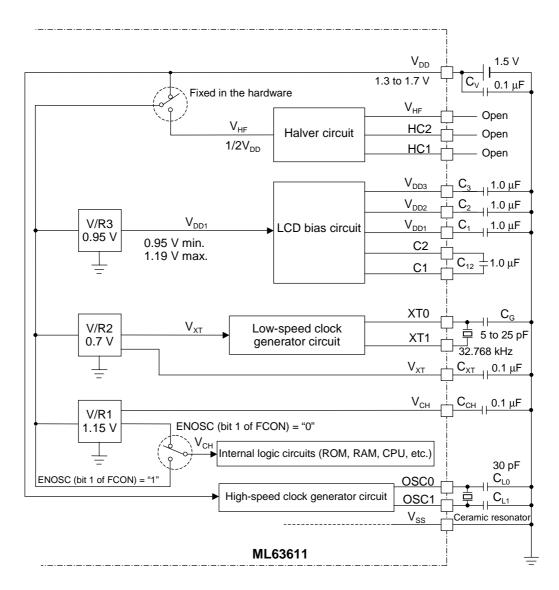

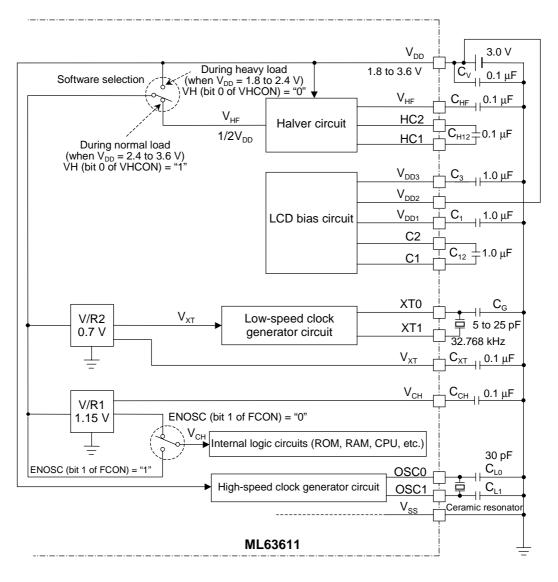

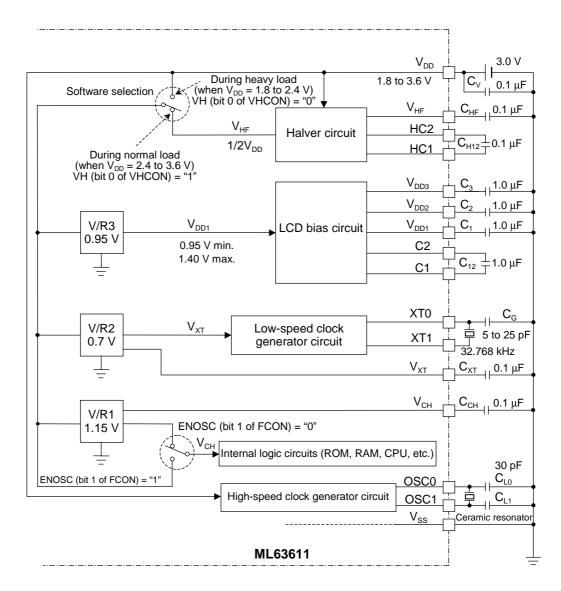

Block diagrams of the ML63611 are shown in Figures 1-1, 1-2, 1-3 and 1-4.

Asterisks (\*) indicate port secondary functions.

Asterisks (\*) indicate port secondary functions.

Figure 1-3 OPTION C Block Diagram

Asterisks (\*) indicate port secondary functions.

Figure 1-4 OPTION D Block Diagram

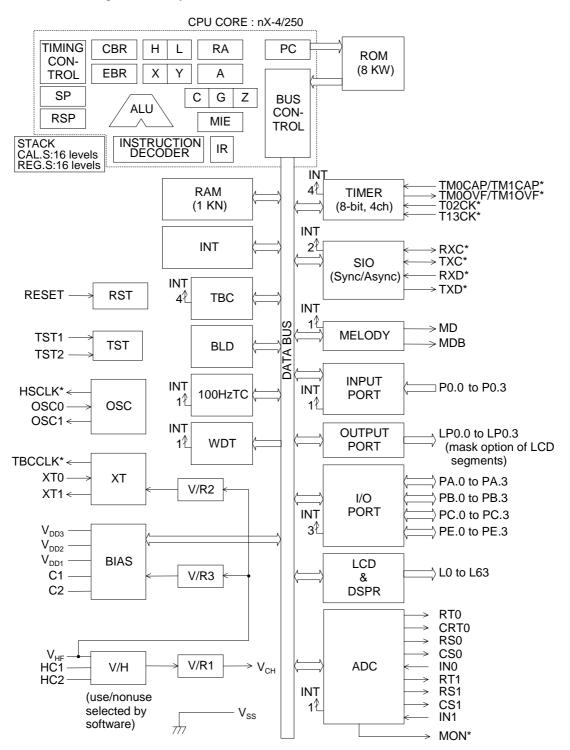

## 1.6 Pin Configuration

## 1.6.1 ML63611 Pin Configuration

The ML63611 chip pin configuration and pad coordinates are shown in Figures 1-5 and Table 1-2 respectively.

Do not bond pins 100 to 112 (marked by "■"). Leave them open.

| Pad No. | Pad Name | X (μm)  | Υ (μm)    | Pad No. | Pad Name        | Chip center:<br>X (µm) | Υ (μm)    |

|---------|----------|---------|-----------|---------|-----------------|------------------------|-----------|

| 1       | L63      | , (µm)  | i (parti) | 34      | IN1             | , (µm)                 | i (parity |

| 2       | L62      |         |           | 35      | CS1             |                        |           |

| 3       | L61      |         |           | 36      | RS1             |                        |           |

| 4       | L60      |         |           | 37      | RT1             |                        |           |

| 5       | L59      |         |           | 38      | V <sub>DD</sub> |                        |           |

| 6       | L58      |         |           | 39      | TST1            |                        |           |

| 7       | L57      |         |           | 40      | TST2            |                        |           |

| 8       | L56      |         |           | 41      | MD              |                        |           |

| 9       | L55      |         |           | 42      | MDB             |                        |           |

| 10      | L54      |         |           | 43      | P0.0            |                        |           |

| 11      | L53      |         |           | 44      | P0.1            |                        |           |

| 12      | L52      |         |           | 45      | P0.2            |                        |           |

| 13      | L51      |         |           | 46      | P0.3            |                        |           |

| 14      | L50      |         |           | 47      | PA.0            |                        |           |

| 15      | L49      | Undeter | mined     | 48      | PA.1            | Undeterr               | mined     |

| 16      | L48      |         |           | 49      | PA.2            |                        |           |

| 17      | L47      |         |           | 50      | PA.3            |                        |           |

| 18      | L46      |         |           | 51      | PB.0            |                        |           |

| 19      | L45      |         |           | 52      | PB.1            |                        |           |

| 20      | L44      |         |           | 53      | PB.2            |                        |           |

| 21      | L43      |         |           | 54      | PB.3            |                        |           |

| 22      | L42      |         |           | 55      | PC.0            |                        |           |

| 23      | L41      |         |           | 56      | PC.1            |                        |           |

| 24      | L40      |         |           | 57      | PC.2            |                        |           |

| 25      | L39      |         |           | 58      | PC.3            |                        |           |

| 26      | L38      |         |           | 59      | PE.0            |                        |           |

| 27      | L37      |         |           | 60      | PE.1            |                        |           |

| 28      | L36      |         |           | 61      | PE.2            |                        |           |

| 29      | RT0      |         |           | 62      | PE.3            |                        |           |

| 30      | CRT0     |         |           | 63      | V <sub>SS</sub> |                        |           |

| 31      | RS0      |         |           | 64      | L35             |                        |           |

| 32      | CS0      |         |           | 65      | L34             |                        |           |

| 33      | IN0      |         |           | 66      | L33             |                        |           |

## Table 1-2 ML63611 Pad Coordinates

| Υ (μm)  | X (μm)   | Pad Name        | Pad No. | Υ (μm) | X (μm)   | Pad Name | Pad No. |

|---------|----------|-----------------|---------|--------|----------|----------|---------|

|         |          | L1              | 98      |        |          | L32      | 67      |

|         |          | L0              | 99      |        |          | L31      | 68      |

|         |          | TRIMB5          | 100     |        |          | L30      | 69      |

|         |          | TRIMB4          | 101     |        |          | L29      | 70      |

|         |          | TRIMB3          | 102     |        |          | L28      | 71      |

|         |          | TRIMDB1         | 103     |        |          | L27      | 72      |

|         |          | TRIMB2          | 104     |        |          | L26      | 73      |

|         |          | TRIMB1          | 105     |        |          | L25      | 74      |

| nection | No-coni  | TRIMB0          | 106     |        |          | L24      | 75      |

|         |          | TRIMDB2         | 107     |        |          | L23      | 76      |

|         |          | TRIM3           | 108     |        |          | L22      | 77      |

|         |          | TRIM2           | 109     |        |          | L21      | 78      |

|         |          | TRIMD           | 110     |        |          | L20      | 79      |

|         | TRIM1    | 111             |         |        | L19      | 80       |         |

|         |          | TRIM0           | 112     |        |          | L18      | 81      |

|         |          | $V_{DD1}$       | 113     |        |          | L17      | 82      |

|         |          | $V_{DD2}$       | 114     |        |          | L16      | 83      |

| nined   | Undeterr | $V_{DD3}$       | 115     | mined  | Undeterr | L15      | 84      |

|         |          | C1              | 116     |        |          | L14      | 85      |

|         |          | C2              | 117     |        |          | L13      | 86      |

|         |          | V <sub>CH</sub> | 118     |        |          | L12      | 87      |

|         |          | V <sub>XT</sub> | 119     |        |          | L11      | 88      |

|         |          | V <sub>HF</sub> | 120     |        |          | L10      | 89      |

|         |          | HC1             | 121     |        |          | L9       | 90      |

|         |          | HC2             | 122     |        |          | L8       | 91      |

|         |          | V <sub>SS</sub> | 123     |        |          | L7       | 92      |

|         |          | OSC1            | 124     |        |          | L6       | 93      |

|         |          | OSC0            | 125     |        |          | L5       | 94      |

|         |          | RESET           | 126     |        |          | L4       | 95      |

|         |          | XT1             | 127     |        |          | L3       | 96      |

|         |          | XT0             | 128     |        |          | L2       | 97      |

|         |          | V <sub>DD</sub> | 129     | ·      |          | 1        | 1       |

Table 1-2 ML63611 Pad Coordinates (continued)

## 1.7 Pin Descriptions

### 1.7.1 Descriptions of the Basic Functions of Each Pin

The basic functions of each pin of the ML63611 are listed in Table 1-3. Use of a slash ("/") in a pin name indicates that the pin has a secondary function. See Table 1-4 for the secondary functions.

In the I/O column, "—" indicates a power supply pin, "I" indicates an input pin, "O" indicates an output pin, and "I/O" indicates an input/output pin.

| Classification | Pin<br>name      | Pad No. | I/O | Function                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                               |

|----------------|------------------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | $V_{DD}$         | 38, 129 |     | Positive power supply                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                               |

|                | V <sub>SS</sub>  | 63, 123 |     | Negative power supply                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                               |

|                | V <sub>DD1</sub> | 113     |     | Power supply pins for LCD bias voltage (internally                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                               |

|                | V <sub>DD2</sub> | 114     |     | generated):                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |

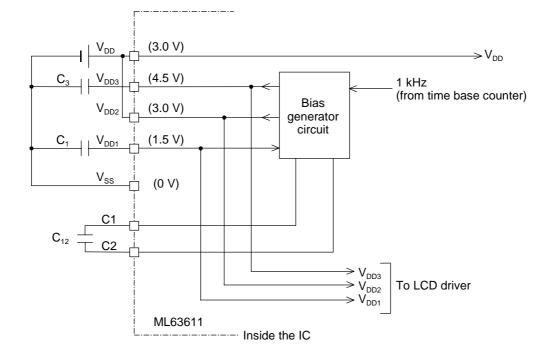

|                | V <sub>DD3</sub> | 115     |     | A capacitor (1.0 $\mu$ F) should be connected between V <sub>DD1</sub><br>and V <sub>SS</sub> , between V <sub>DD2</sub> and V <sub>SS</sub> , and between V <sub>DD3</sub> and V <sub>SS</sub><br>For the OPTION A, connect V <sub>DD1</sub> with V <sub>DD</sub> ; for the OPTION<br>C, connect V <sub>DD2</sub> with V <sub>DD</sub> . |                                                                                                                                                                                               |

|                | C1               | 116     |     | Capacitor connection pins for LCD bias voltage                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                               |

|                | C2               | 117     |     | generation: A capacitor (1.0 $\mu$ F) should be connected between C1 and C2.                                                                                                                                                                                                                                                              |                                                                                                                                                                                               |

| Power Supply   | V <sub>HF</sub>  | 120     |     | _                                                                                                                                                                                                                                                                                                                                         | Power supply pin for the internal regulator:<br>A capacitor (0.1 $\mu$ F) should be connected between this pir<br>and V <sub>SS</sub> . Leave this pin open for the OPTION A and<br>OPTION B. |

|                | V <sub>XT</sub>  | 119     |     |                                                                                                                                                                                                                                                                                                                                           | Power supply pin for the voltage regulator circuit for low-<br>speed oscillation:<br>A capacitor (0.1 $\mu$ F) should be connected between this pir                                           |

|                |                  |         |     | and $V_{ss}$ .                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                               |

|                | N                | 110     |     | Power supply pin for the voltage regulator circuit for internal logic:                                                                                                                                                                                                                                                                    |                                                                                                                                                                                               |

|                | V <sub>CH</sub>  | 118     |     | A capacitor $C_1$ (0.1 $\mu F)$ should be connected between this pin and $V_{SS}$                                                                                                                                                                                                                                                         |                                                                                                                                                                                               |

|                | HC1              | 121     |     | Capacitor connection pins for the halver circuit:                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                               |

|                | HC2              | 122     |     | A capacitor (0.1 $\mu$ F) should be connected between HC1 and HC2. Leave these pins open for the OPTION A and OPTION B.                                                                                                                                                                                                                   |                                                                                                                                                                                               |

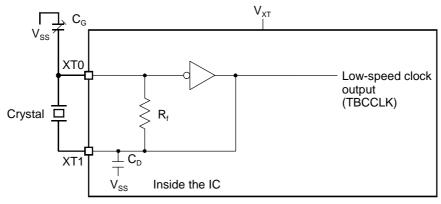

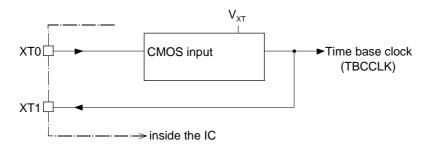

|                | XT0              | 128     | I   | Low-speed clock oscillation pins:                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                               |

|                | XT1              | 127     | 0   | Connect a crystal between XT0 and XT1, and connect capacitor ( $C_G$ ) between XT0 and $V_{SS}$ .                                                                                                                                                                                                                                         |                                                                                                                                                                                               |

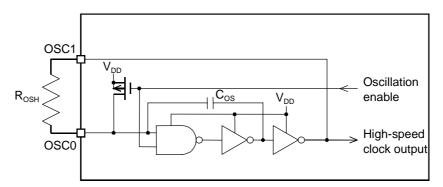

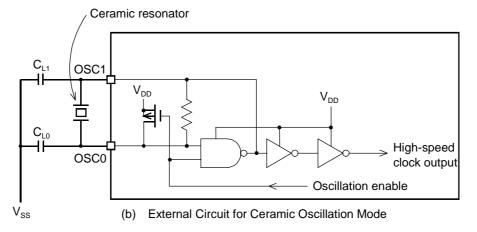

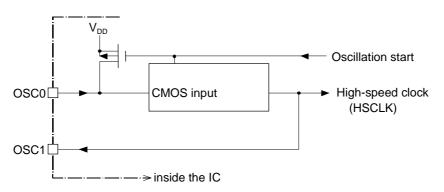

|                | OSC0             | 125     | I   | High-speed clock oscillation pins:                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                               |

| Oscillation    | OSC1             | 124     | 0   | Ceramic oscillation or RC oscillation is selected by the software. In the OPTION A and OPTION B, only RC oscillation is available.<br>If ceramic oscillation is selected, connect a ceramic resonator between OSC0 and OSC1, and connect capacitor ( $C_{L0}$ , $C_{L1}$ ) between OSC0 and $V_{SS}$ and between OSC1 and $V_{SS}$ .      |                                                                                                                                                                                               |

|                |                  |         |     | If RC oscillation is selected, connect external oscillation resistor ( $R_{OSH}$ ) between OSC0 and OSC1.                                                                                                                                                                                                                                 |                                                                                                                                                                                               |

| Test           | TST1             | 39      | 1   | Input pins for testing:                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                               |

| 1000           | TST2             | 40      |     | A pull-down resistor is internally connected to these pins.                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |

Table 1-3 Pin Description (Basic Functions)

| Classification | Pin<br>name | Pad No. | I/O  | Function                                                                                                                                                                                                                                                                                                  |

|----------------|-------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

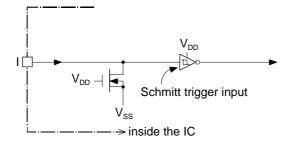

| Reset          | RESET       | 126     | I    | Reset input pin:<br>2 kHz sampling circuit is equipped.<br>Holding this pin to "H" level for 1 ms or more puts this<br>device into a reset state. Then, setting this pin to "L" level<br>starts executing an instruction from address 0000H.<br>A pull-down resistor is internally connected to this pin. |

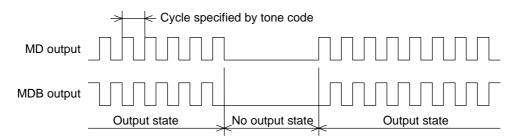

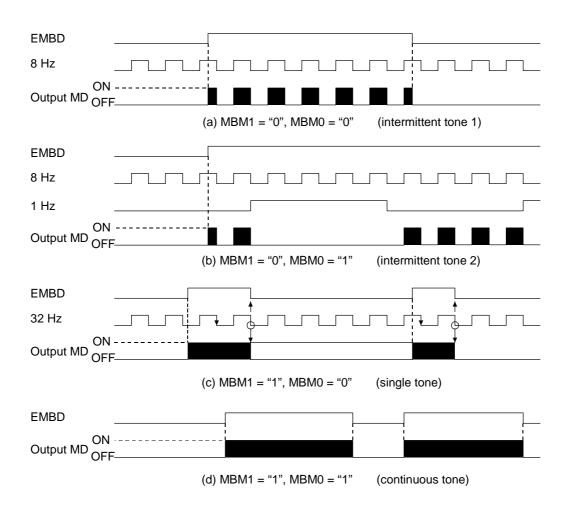

|                | MD          | 41      |      | Melody output pin (non-inverted output)                                                                                                                                                                                                                                                                   |

| Melody         | MDB         | 42      | Ο    | Melody output pin (inverted output): $V_{\text{DD}}$ or $V_{\text{SS}}$ is selectable for the pin output voltage when melody output is turned off.                                                                                                                                                        |

|                | P0.0        | 43      |      | 4-bit input port: Pull-up resistor input, pull-down resistor                                                                                                                                                                                                                                              |

|                | P0.1        | 44      |      | input, or high-impedance input is selectable for each bit.                                                                                                                                                                                                                                                |

|                | P0.2        | 45      |      | A system reset function is provided that resets the system<br>when there is a simultaneous key depression of multiple                                                                                                                                                                                     |

|                | P0.3        | 46      |      | bits.                                                                                                                                                                                                                                                                                                     |

|                | PA.0        | 47      | I/O  | 4-bit input-output ports:                                                                                                                                                                                                                                                                                 |

|                | PA.1        | 48      |      | In input mode, pull-up resistor input, pull-down resistor input, or high-impedance input is selectable for each bit.                                                                                                                                                                                      |

|                | PA.2        | 49      |      |                                                                                                                                                                                                                                                                                                           |

|                | PA.3        | 50      |      | In output mode, P-channel open drain output, N-channel                                                                                                                                                                                                                                                    |

|                | PB.0        | 51      |      | open drain output, CMOS output, or high-impedance                                                                                                                                                                                                                                                         |

| Port           | PB.1        | 52      |      | output is selectable for each bit.                                                                                                                                                                                                                                                                        |

|                | PB.2        | 53      | ., 0 |                                                                                                                                                                                                                                                                                                           |

|                | PB.3        | 54      |      | 4                                                                                                                                                                                                                                                                                                         |

|                | PC.0        | 55      |      |                                                                                                                                                                                                                                                                                                           |

|                | PC.1        | 56      | I/O  |                                                                                                                                                                                                                                                                                                           |

|                | PC.2        | 57      |      |                                                                                                                                                                                                                                                                                                           |

|                | PC.3        | 58      |      | 4                                                                                                                                                                                                                                                                                                         |

|                | PE.0        | 59      |      |                                                                                                                                                                                                                                                                                                           |

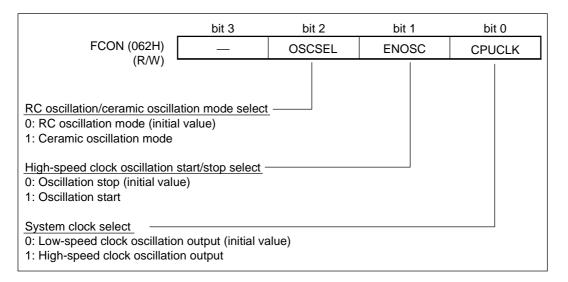

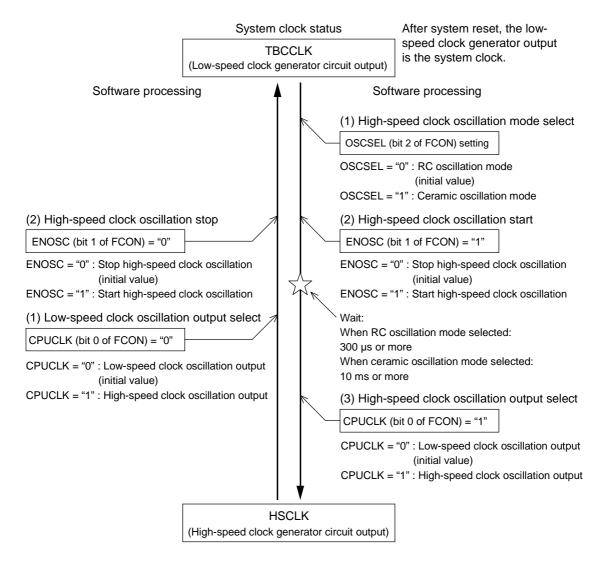

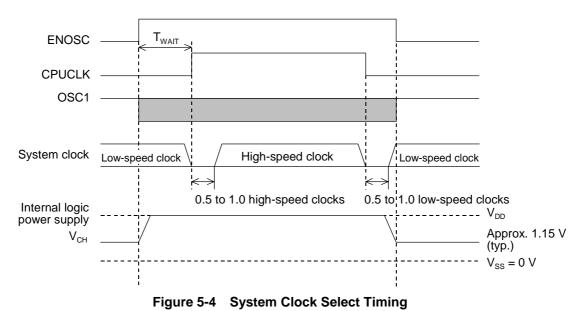

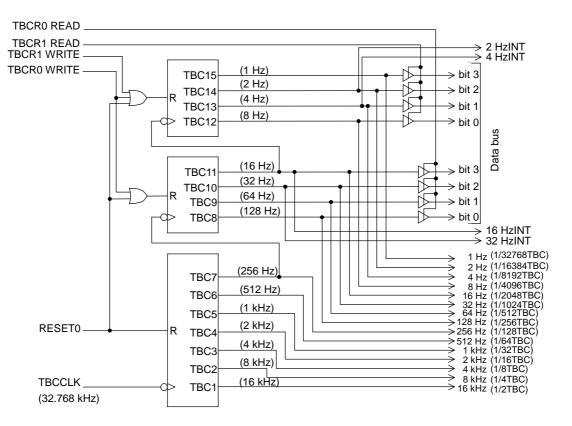

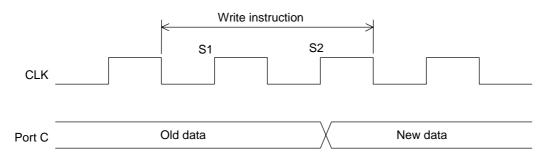

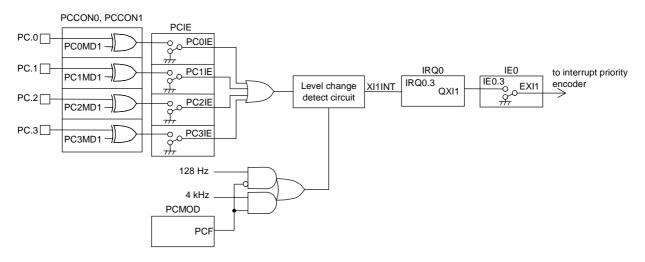

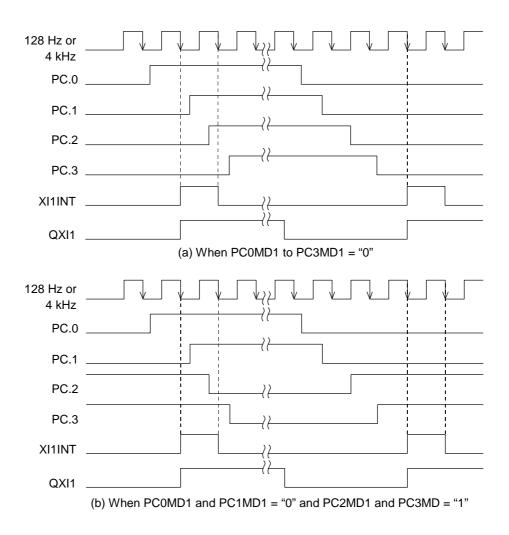

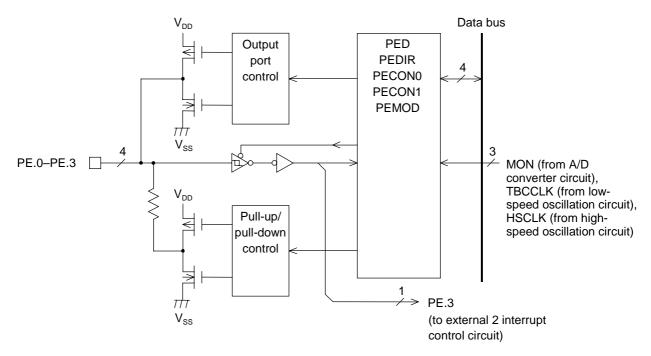

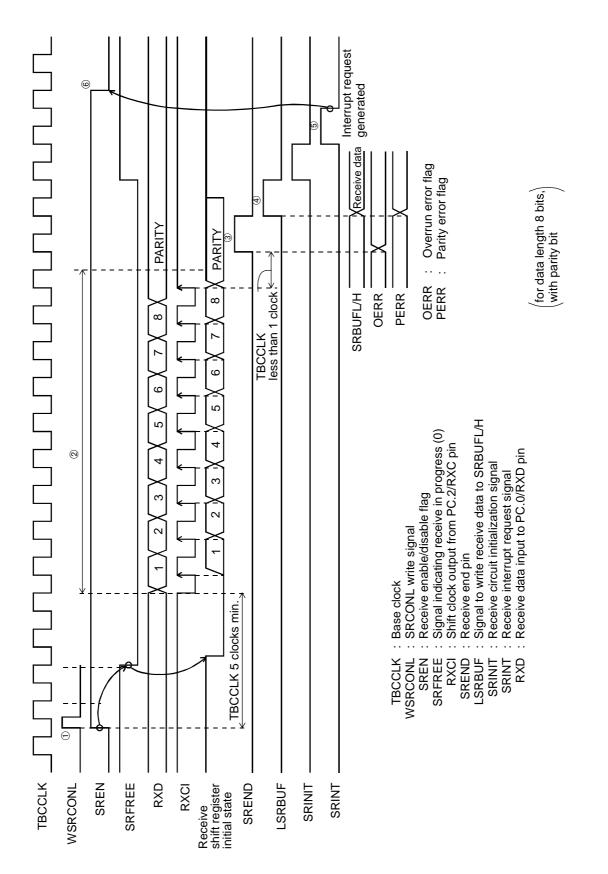

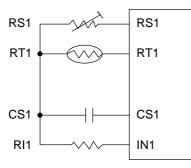

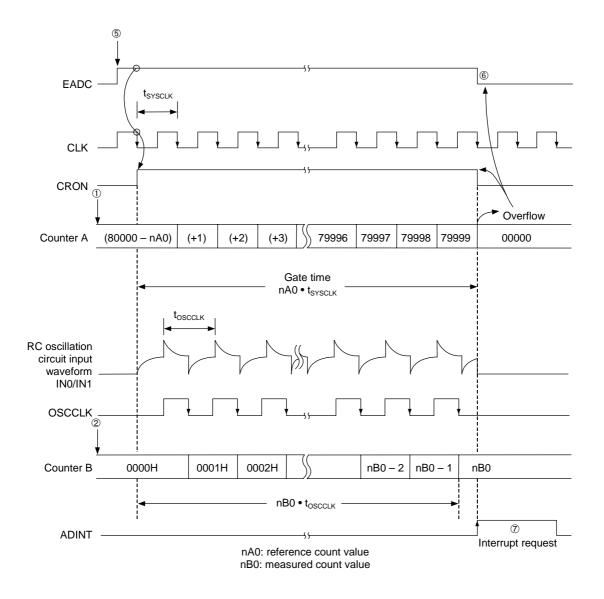

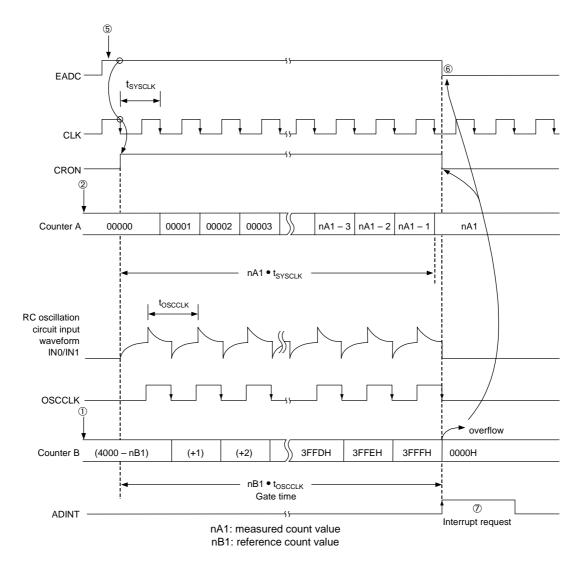

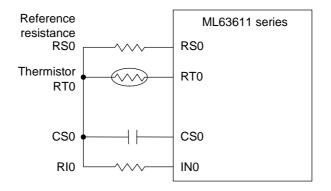

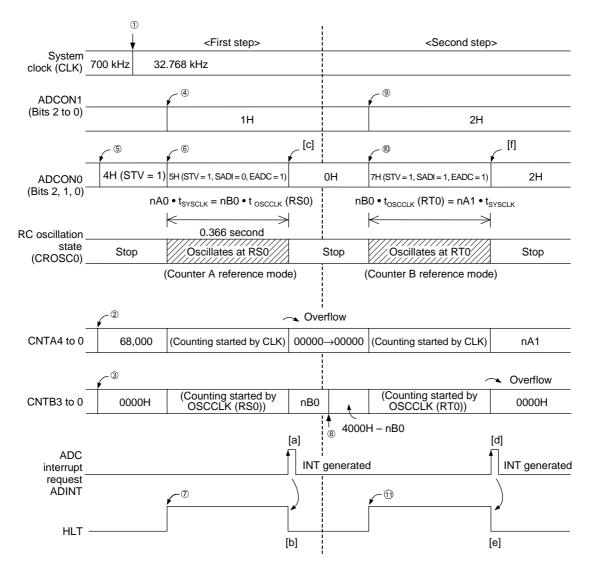

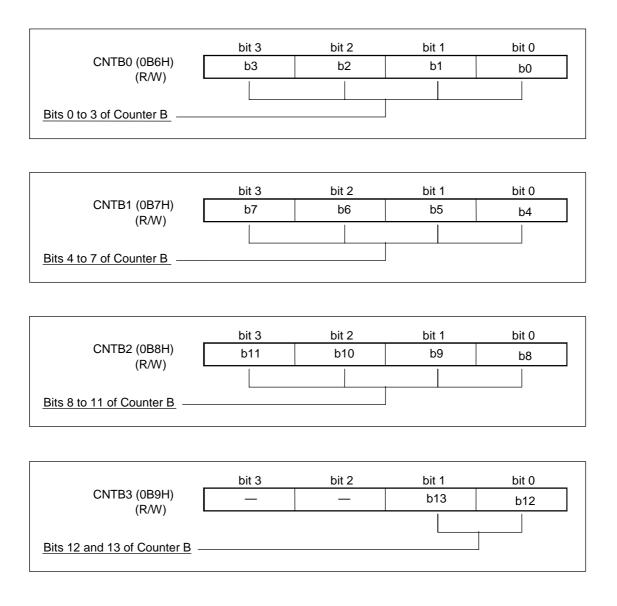

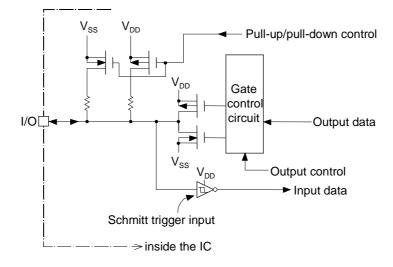

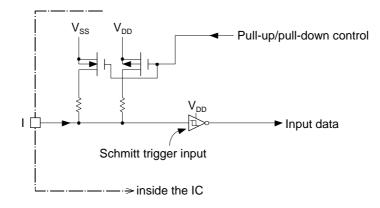

|                | PE.1        | 60      | I/O  |                                                                                                                                                                                                                                                                                                           |