# RETICON®

# RA1133J Full Frame CCD Image Sensor

24 µm square pitch, 1100 x 330 pixel configuration

## Description

The RA1133J is a full frame CCD sensor with reset capabilities designed specifically for use in spectroscopy, biomedical imaging and related scientific imaging applications. The package for the array is designed with an integrated two stage thermoelectric cooler. This enables the device to be run 40° C below ambient temperature, -15° C when compared to room temperature. Its combination of very low noise and low dark current make it ideal for low light, high dynamic range and high resolution applications.

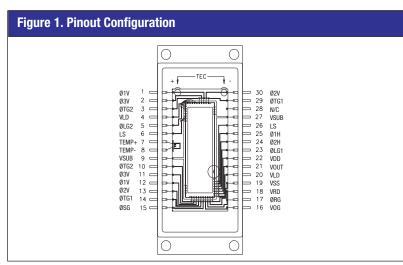

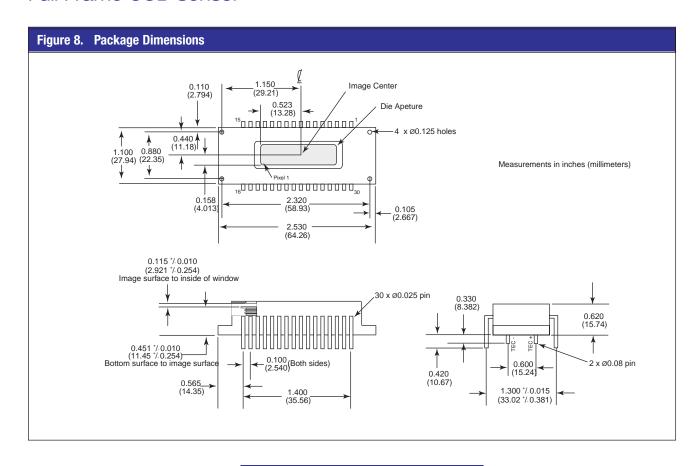

The imager is structured with a single output register at one end of the imaging columns. A lateral reset drain is located adjacent to this readout register which enables the dumping of accumulated charge from the array. Two phase clocks are needed to drive the readout register. Three phase clocks are needed to drive imaging cells. The array is available in a 30-pin metal package with an integrated TE cooler as shown in Figure 1. Package dimensions are shown in Figure 8.

# **MPP Operation**

A major source of dark current in devices such as this originates in surface states at the Si-SiO2 interface. A unique design and process enables the RA1133J to be run in "multi-pinned phase" or MPP mode of operation. This helps eliminate dark current generation in the interface surface states. By holding the vertical clocks at negative potential during integration and horizontal signal readout, the surface will not be depleted and the surface state will not generate dark current.

Caution: While the RA1133J imagers have been designed to resist electrostatic discharge (ESD), they can be damaged from such discharges. Always observe proper ESD precautions when handling and storing these sensors.

#### **Features**

- 363,000 picture elements (pixels) in a 1100 x 330 configuration

- 24 µm square pixels

- 2-phase buried channel process

- On-chip amplifier for low noise and high speed readout

- Dynamic range greater than 25,000:1

- On-chip temperature sensor

- Two stage TE cooler integrated into the package

- Hermetically sealed

- 100% fill factor

- 10 MHz data rate

# **Imaging Area**

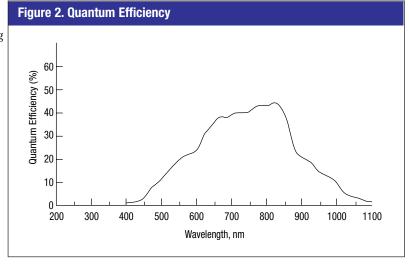

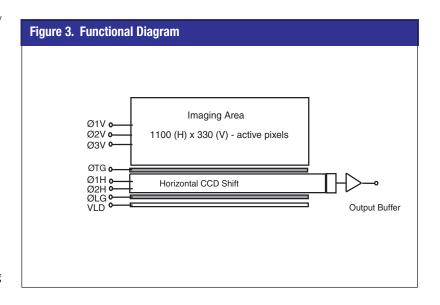

The imaging area is an array of 1100 columns (vertical CCD shift registers). Each column has 330 picture elements. The pixel size is 24  $\mu m$  by 24  $\mu m$ . The total imaging area is 26.4 mm by 7.92 mm. Typical spectral response as a function of wavelength is shown in Figure 2. This is for both the standard array and an array coated with lumogen, an UV phosphor that extends the range of the detector into the ultraviolet.

In the vertical direction, each pixel corresponds to one stage (three electrodes) of the shift register. The three electrode groups are driven by three-phases (Ø1V -Ø3V) brought in from both edges of the array to improve clock electrode response time. Charge packets (imaging data) in the vertical register can be shifted to the horizontal readout by clocking the three phases (Ø1V, Ø2V and Ø3V). A transfer gate (ØTG) is provided at the interface of the vertical register. The transfer gate controls the transferring of charge into the horizontal readout register. Charge flow is from Ø3 gate of the vertical shift register into Ø1 gate of the horizontal readout register. The control function is performed by pulsing the transfer gate high to permit the charge flow from the vertical register into the horizontal register for readout. When the potential of the vertical register electrodes is held steady, a potential well is created beneath the storage gates Ø1V and Ø2V. When an image impinges on the sensing area, an electrical signal of the scene will be collected in the potential well during this integration period.

Following the integration interval, the collected charge (signal) in the array can be read out as a full frame image by transferring the charge, one or more rows at a time, into the horizontal shift register. From here, the charge can be shifted serially to the output amplifier. A mechanical shutter is needed to shield the array from incident light during the readout process. A strobe illumination could be used to stimulate the shuttered mode of operation. Image smearing degrades the performance, particularly at low data rates, unless shuttering is provided.

## Horizontal Register

The horizontal shift register is driven by two phase clocks (Ø1H and Ø2H). The horizontal register has 1100 stages plus an extension of 35 stages ( 3 dummy stages, 16 leading isolation stages and 16 trailing isolation stages). As a result, amplifier power is dissipated more efficiently and dark current generation by localized heating is minimized.

### **Summing Mode**

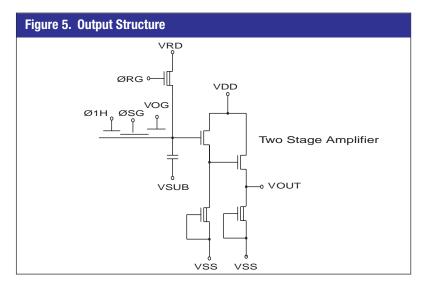

At the end of the horizontal register, there is an ouput summing well which can be clocked to allow multiple-pixel summation of the scene. This summing well is located after the 19 extra stages of the horizontal register and prior to the DC biased gate (VOG) as shown in Figure 5. The summing gate (ØSG) can be clocked with one of the horizontal clock phases or with its own clock generator (see Figure 4a for summing gate timing). For example, two parallel lines of charge are additively transferred into the serial register, then the summing gate is pulsed low after the charge from two serial pixels has been transferred into the summing well. Thus, the resulting signal represents the sum of charges in four (2x2) contiguous pixels from the imaging region. It effectively reduces the 1100 x 330 device to a 550 x 165 array and increases the pixel size by four times. Other variations of this technique can be useful for low-light level situations, i.e., scenes with low contrast or a low signal-tonoise ratio. There is, of course, a loss in resolution that accompanies the gain in effective pixel size.

## **Output Amplifier**

There is an on-chip amplifier that is located at the end of the extended shift register. The amplifier is a two stage buried channel transistor amplifier as shown in Figure 5. It is designed to operate with data rates in excess of 10 MHz. It has a bandwidth of approximately 60 MHz with a 10 pF load.

## **Temperature Monitoring**

The RA1133J device has a temperature sensor integrated into the package for monitoring array temperature.

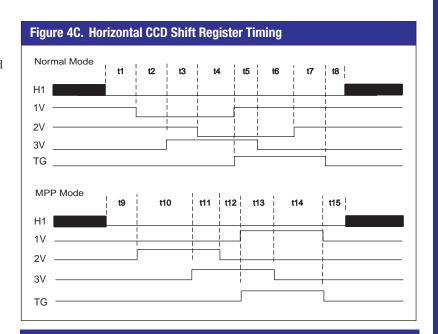

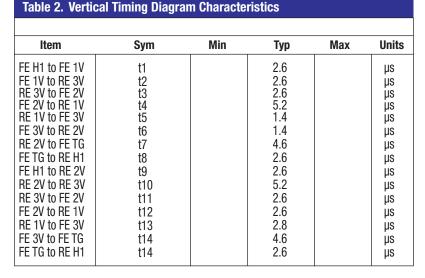

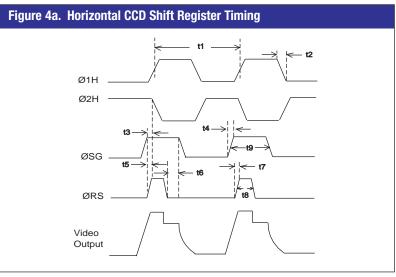

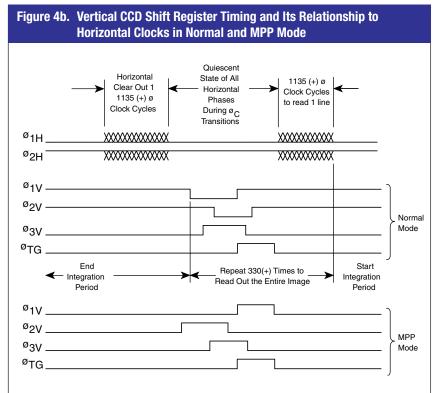

#### **Timing Requirements**

The timing recommended to run the RA1133J imager in the low speed and low noise mode of operation is shown in Figures 4A, 4B, and 4C. A 50% duty cycyle, two phase clock will drive the horizontal register to its highest speed. Figure 4a shows the timing of the horizontal two phase clocks, summing well clock and reset clock. To achieve high charge transfer, serial clocks must cross between 10% and 90% of the peak voltage. In addition, the rise and fall times of the two phase clocks need to be more than 50 ns in order to prevent the injection of spurious charge into the CCD channel.

# Timing Requirements (cont.)

The timing shown in Figure 4a is repeated 1100 + 35 (or more) times to allow the readout of one complete line of the image.

Figure 4b shows the timing requirements for the vertical register. Overlapping of the vertical clocks are normally longer than 5 µs. Rise and fall times of all clocks need to be 3 µs or longer in order to prevent spurious charge into the CCD channel. All vertical clock transitions should occur when the horizontal clocks are held steady.

Timing for MPP and normal mode is shown. The difference between the two modes is that during integration, all clocks must be held low for MPP mode.

#### **Array Cooling**

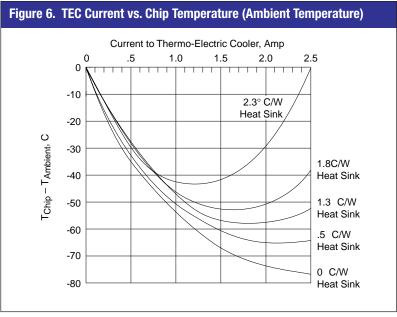

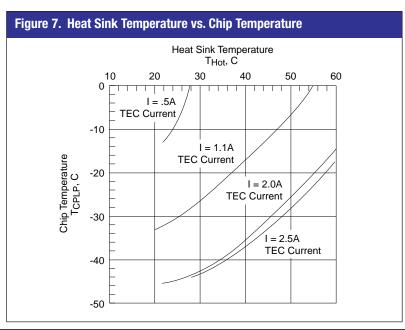

Both the dark current and the noise performance of the array can be improved by cooling. The dark current will be reduced by 50% for approximately every 6 - 8 ° C reduction in array temperature. Cooling can be achieved via the integrated thermoelectric cooler. The bias supplies TEC+ and TEC- electronically control this cooler. This is a two-stage cooler capable of reducing the temperature of the array 40° C from the ambient temperature. Additional cooling can be achieved by decreasing the ambient temperature or by cooling the heat sink on the TE cooler as shown in Figure 6 and Figure 7.

### **Region of Interest**

Rapid access to regions of interest is facilitated by use of a lateral charge drain. The drain is constructed adjacent to the horizontal CCD (HCCD) shift register. Unwanted lines of data are quickly disposed without the requirement for horizontal transfer. In this manner, entire lines of image data can be disposed of by a single vertical shift sequence, with a time penalty of 20 µs. This is to be contrasted with the normal read sequence which includes both the vertical shift (20 µs), plus readout of the 1130 horizontal elements (2260 µs). As the unwanted lines are transferred from storage region into the HCCD, the horizontal phases are held high to maintain a surface

potential which is more positive than the low state channel potential of the transfer gate. Similar to a lateral antiblooming drain, charge will spill preferentially into the rapid discharge drain. Due to the fixed potential barrier, the HCCD cannot be completely cleared of charge and thus one horizontal shift sequence is required before resumption of valid data read.

| Table 1. Timing D                                         | liagram Chara | icteristics |     |     |       |

|-----------------------------------------------------------|---------------|-------------|-----|-----|-------|

| Item                                                      | Sym           | Min         | Тур | Max | Units |

| $\mathbf{Ø}_{_{1,2H}}$ rise/fall time                     | T1            |             | 50  |     | ns    |

| $\mathbf{Ø}_{_{1,\mathrm{2H}}}$ clock period              | T2            |             |     | 100 | ns    |

| $\emptyset_{\rm SG}$ delay from $\emptyset_{\rm H2}$ edge | Т3            | +0          |     |     | ns    |

| $\phi_{_{\rm SG}}$ rise/fall time                         | T4            |             | 50  |     | ns    |

|                                                           | T5            | +0          |     |     | ns    |

| $ \emptyset_{SG} $ delay from $ \emptyset_{RG} $ edge     | T6            | +0          |     |     | ns    |

| Ø <sub>RG</sub> rise/fall time                            | T7            |             | 50  |     | ns    |

| Ø <sub>RG</sub> pulse duration                            | Т8            | 10          |     |     | ns    |

| $\emptyset_{\scriptscriptstyle{SG}}$ pulse duration       | Т9            |             |     | 100 | ns    |

| Table 3. Absolute Maximum Ratings            |                |                |  |

|----------------------------------------------|----------------|----------------|--|

|                                              | Min            | Max            |  |

| Storage Temperature<br>Operating Temperature | - 55C<br>- 55C | + 85C<br>+ 85C |  |

| Parameter                     | Sym       | Min    | Тур         | Max | Units  |

|-------------------------------|-----------|--------|-------------|-----|--------|

| Format                        |           |        | 1100 x 330  |     |        |

| Pixel Size                    |           |        | 24 x 24     |     | μm     |

| Imaging Area                  |           |        | 26.4 x 7.92 |     | mm     |

| Dynamic Range <sup>1</sup>    | DR        |        | 25,000:1    |     |        |

| Full Well Charge <sup>2</sup> | $Q_SAT$   | 250    | 300         |     | Ke-    |

| Saturation Voltage            | $V_{SAT}$ | 1000   | 1200        |     | m۷     |

| Dark Current MPP 3            | DL        |        | 1           | 3   | pA/cm2 |

| Photo Response                | PRNU      |        | 5           | 10  | ±%     |

| Non Uniformity                |           |        |             |     |        |

| Dark Signal Uniformity        | DSNU      |        | 2           | 5   | ±%     |

| Charge Transfer Efficiency    | CTE       | 0.9999 | 0.99995     |     |        |

| Output Amplifier Gain         |           |        | 4           |     | μV/e-  |

| Operating Frequency           | fclock    |        |             | 15  | MHz    |

| Read Noise 4                  |           |        | 10          |     | e-     |

#### Notes:

- 1. Full well/read noise, MPP mode

- 2. RLoad = 5.1 kOhms, MPP mode

- 3. MPP mode at -15 ℃

- 4. Measured at 500 kHz at -15 ℃

| Table 5. Rec  | Table 5. Recommended Operating Conditions |                            |             |          |           |

|---------------|-------------------------------------------|----------------------------|-------------|----------|-----------|

| Pin #         | Signal                                    | Function                   |             | Тур      | Tolerance |

| 24, 25        | Ø1H, Ø2H                                  | Horizontal Clocks          | High<br>Low | 5        | ±5%       |

| 3, 29         | ØTG                                       | Transfer Gate Clock        | High<br>Low | 4 -8     | ±10%      |

| 15            | ØSG                                       | Summing Gate Clock         | High<br>Low | 5<br>0   | ±5%       |

| 1, 12         | Ø1V (MPP)                                 | Vertical Clock (MPP Phase) | High<br>Low | 4<br>-9  | ±5%       |

| 2, 11, 13, 30 | Ø2V, Ø3V                                  | Vertical Clocks            | High<br>Low | 2<br>-11 | ±5%       |

| 5, 23         | ØLG                                       | Lateral Charge Gate        | High<br>Low | 5<br>0   | ±5%       |

| 17            | ØRG                                       | Reset Gate                 | High<br>Low | 8        | ±10%      |

| 16            | VOG                                       | Output Gate                |             | 3        | ±5%       |

| 22            | VDD                                       | Amplifier Voltage Supply   |             | 14       | ±5%       |

| 4, 20         | VLD                                       | Lateral Charge Drain       |             | 13       | ±5%       |

| 18            | VRD                                       | Amplifier Reset Drain      |             | 10       | ±5%       |

| 6, 26         | LS                                        | Light Shield               |             | GND      | ±5%       |

| 19            | VSS                                       | Video Amplifier Source     |             | GND      | ±5%       |

| 9, 27         | VSUB                                      | Substrate Bias             |             | -2       | ±5%       |

| Pin # | Sym               | Function              | Pin# | Sym               | Function               |

|-------|-------------------|-----------------------|------|-------------------|------------------------|

| 1     | Ø <sub>1V</sub>   | Vertical Phase 1      | 16   | V <sub>og</sub>   | Output Gate            |

| 2     | Ø <sub>3V</sub>   | Vertical Phase 3      | 17   | $\emptyset_{RG}$  | Reset Gate             |

| 3     | $\emptyset_{TG2}$ | Transfer Gate 2       | 18   | $V_{RD}$          | Reset Drain            |

| 4     | $V_{LD}$          | Lateral Charge Drain  | 19   | V <sub>SS</sub>   | Video Amplifier Source |

| 5     | $\emptyset_{LG2}$ | Lateral Charge Gate 2 | 20   | V <sub>LD</sub>   | Lateral Charge Drain   |

| 6     | LS                | Light Shield          | 21   | V <sub>out</sub>  | Video Output           |

| 7     | TEMP+             | Temp+                 | 22   | $V_{DD}$          | Video Amplifier Drain  |

| 8     | TEMP-             | Temp-                 | 23   | Ø <sub>LG1</sub>  | Lateral Charge Gate 1  |

| 9     | $V_{SUB}$         | Substrate             | 24   | Ø <sub>2H</sub>   | Horizontal Phase 2     |

| 10    | Ø <sub>TG2</sub>  | Transfer Gate 2       | 25   | Ø <sub>1H</sub>   | Horizontal Phase 1     |

| 11    | Ø <sub>3V</sub>   | Vertical Phase 3      | 26   | LS                | Light Shield           |

| 12    | Ø <sub>1V</sub>   | Vertical Phase 1      | 27   | $V_{SUB}$         | Substrate              |

| 13    | Ø <sub>2V</sub>   | Vertical Phase 2      | 28   | N/C               | No Connection          |

| 14    | Ø <sub>TG1</sub>  | Transfer Gate 1       | 29   | $\emptyset_{TG1}$ | Transfer Gate 1        |

| 15    | Øsg               | Summing Gate          | 30   | Ø <sub>2V</sub>   | Vertical Phase 2       |

# **Ordering Information**

While the information provided in this data sheet is intended to describe the form, fit and function for this product, PerkinElmer reserves the right to make changes without notice.

| Table 7. Ordering Information |               |  |  |

|-------------------------------|---------------|--|--|

| Part Number                   | RA1133JAS-912 |  |  |

For more information e-mail us at opto@perkinelmer.com or visit our web site at www.perkinelmer.com/opto.

All values are nominal; specifications subject to change without notice.

|               | North America                                                                                                                                                            |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| United States | PerkinElmer Optoelectronics<br>2175 Mission College Blvd.<br>Santa Clara, CA 95054<br>Toll Free: 800-775-0PTO (6786)<br>Phone: +1-408-565-0830<br>Fax: +1-408-565-0703   |

|               | Europe                                                                                                                                                                   |

| Germany       | PerkinElmer Optoelectronics GmbH<br>Wenzel-Jaksch-Str. 31<br>D-65199 Wiesbaden, Germany<br>Phone: +49-611-492-570<br>Fax: +49-611-492-165                                |

|               | Asia                                                                                                                                                                     |

| Japan         | PerkinElmer Optoelectronics<br>NEopt. 18F, Parale Mitsui Building 8<br>Higashida-Cho, Kawasaki-Ku<br>Kawasaki-Shi, Kanagawa-Ken 210-0005 Japan<br>Phone: +81-44-200-9170 |

|               | Fax: +81-44-200-9160<br>www.neopt.co.jp                                                                                                                                  |

| Singapore     | 47 Ayer Rajah Crescent #06-12<br>Singapore 139947<br>Phone: +65-770-4925<br>Fax: +65-777-1008                                                                            |